# **TechNexion**

March 6<sup>th</sup> 2011

SOM

# TDM-3730 System on Module

TDM-3730 HARDWARE MANUAL rev A | March 6 2012, TechNexion

TDM-3730 HARDWARE MANUAL rev A

March 6 2012, TechNexion

# TDM-3730

TDM-3730 System on Module

Hardware Manual

Rev A

March 6 2012, TechNexion

## **1** Contents

| 2 | Rev  | vision5     |                                                   |          |  |  |  |  |  |

|---|------|-------------|---------------------------------------------------|----------|--|--|--|--|--|

| 3 | Care | e and       | Maintenance6                                      | 5        |  |  |  |  |  |

|   | 3.1  | 3.1 General |                                                   |          |  |  |  |  |  |

|   | 3.2  | Reg         | ulatory Information6                              | 5        |  |  |  |  |  |

| 4 | Des  | cripti      | on9                                               | )        |  |  |  |  |  |

|   | 4.1  | Bloc        | k Diagram TDM-3730 System on Module10             | )        |  |  |  |  |  |

|   | 4.2  | Fun         | ctional Block Diagram CPU11                       | L        |  |  |  |  |  |

| 5 | Syst | em C        | Components                                        | 2        |  |  |  |  |  |

|   | 5.1  | CPU         | : DM-3730                                         | <u>)</u> |  |  |  |  |  |

|   | 5.1. | 1           | DM-3730 Digital Media Processor Features12        | 2        |  |  |  |  |  |

|   | 5.2  | PMI         | C: TPS-6593015                                    | 5        |  |  |  |  |  |

|   | 5.2. | 1           | TPS-65930 – Introduction                          | 5        |  |  |  |  |  |

|   | 5.2. | 2           | TPS-65930: Features                               | 5        |  |  |  |  |  |

|   | 5.3  | Mer         | nory16                                            | 5        |  |  |  |  |  |

|   | 5.4  | NAN         | ID Flash                                          | 1        |  |  |  |  |  |

|   | 5.5  | Net         | work: SMSC LAN9220                                | 3        |  |  |  |  |  |

|   | 5.6  | USB         | PHY19                                             | )        |  |  |  |  |  |

|   | 5.7  | WiF         | i Module19                                        | )        |  |  |  |  |  |

|   | 5.7. | 1           | WiFi Signals Description                          | )        |  |  |  |  |  |

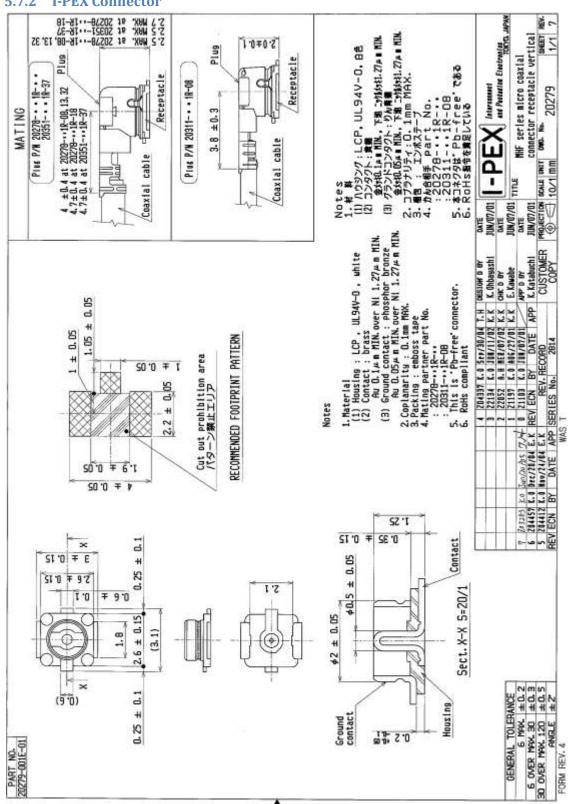

|   | 5.7. | 2           | I-PEX Connector                                   | )        |  |  |  |  |  |

| 6 | Hov  | v to u      | se the Multiplex Mode21                           | L        |  |  |  |  |  |

|   | 6.1  | Mul         | tiplexing in u-boot21                             | L        |  |  |  |  |  |

| 7 | TDN  | 1-373       | 0 Module Pin Description23                        | 3        |  |  |  |  |  |

|   | 7.1. | 1           | Definitions                                       | 3        |  |  |  |  |  |

| 8 | Sign | al De       | scription                                         | )        |  |  |  |  |  |

|   | 8.1  | Exte        | rnal Memory Interfaces – GPMC Signals Description | )        |  |  |  |  |  |

|   | 8.2  | Vide        | eo Interfaces –CAM Signals description40          | )        |  |  |  |  |  |

|   | 8.3  | Vide        | eo Interfaces – DSS Signals Description42         | )        |  |  |  |  |  |

March 6 2012, TechNexion

| 8.4  | Video Interfaces – TV Signals Description43                            |

|------|------------------------------------------------------------------------|

| 8.5  | Serial Communication Interfaces – I <sup>2</sup> C Signals Description |

| 8.6  | Serial Communication Interfaces – McBSP LP Signals Description         |

| 8.7  | Serial Communication Interfaces – McSPI Signals Description45          |

| 8.8  | Serial Communication Interfaces – UARTs Signals Description            |

| 8.9  | Serial Communication Interfaces – USB Signals Description              |

| 8.10 | Removable Media Interfaces – MMC/ SDIO Signals                         |

| 8.11 | General Purpose IOs Signals Description                                |

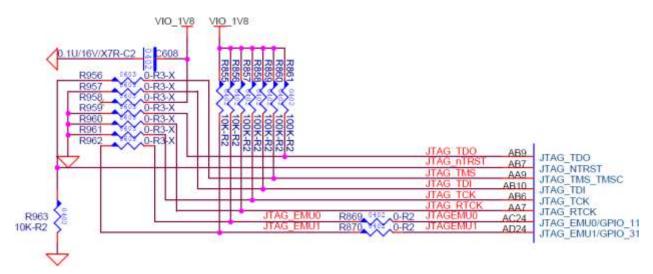

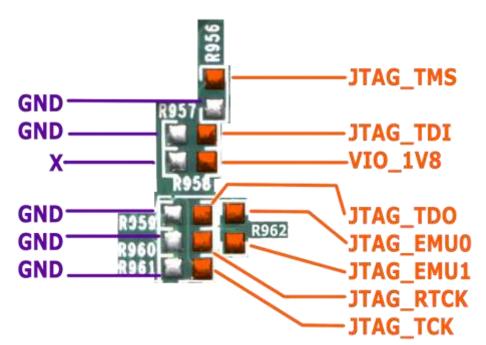

| 8.12 | 2 Test Interfaces – JTAG Signals Description                           |

| 8.13 | Power Supplies Signals description51                                   |

| 8.14 | System and Miscellaneous Signals Description51                         |

| 8.15 | 5 Touch Interupt Signal Description                                    |

| 8.16 | Serial Communcication Interfaces – HDQ/ 1-Wire Signals Description     |

| 8.17 | PWM Signals Description                                                |

| 8.18 | ADC Signals Description                                                |

| 8.19 | Analog Audio Signals Description                                       |

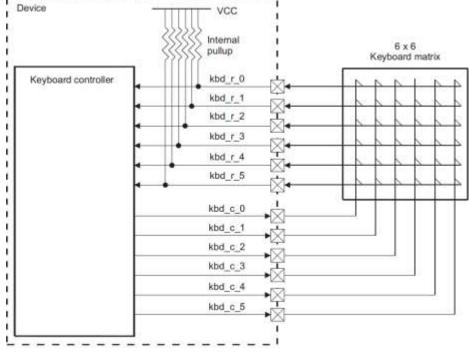

| 8.20 | 0 Keypad Signals Description54                                         |

| 8.21 | Ethernet Signals Description55                                         |

| 8.22 | 2 LED Signals Description                                              |

| 8.23 | Pull-up or Pull-down Signals Description                               |

| 8.24 | Boot Option                                                            |

| 9 E  | lectrical Characteristics                                              |

| 10   | Environmental Specifications                                           |

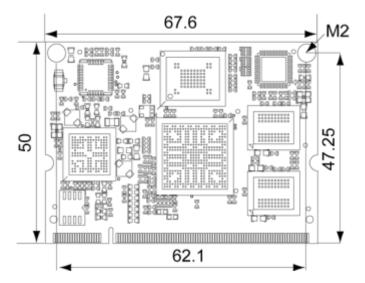

| 11   | Mechanical Dimensions                                                  |

| 11.1 | TDM-3730 System on Module Dimensions                                   |

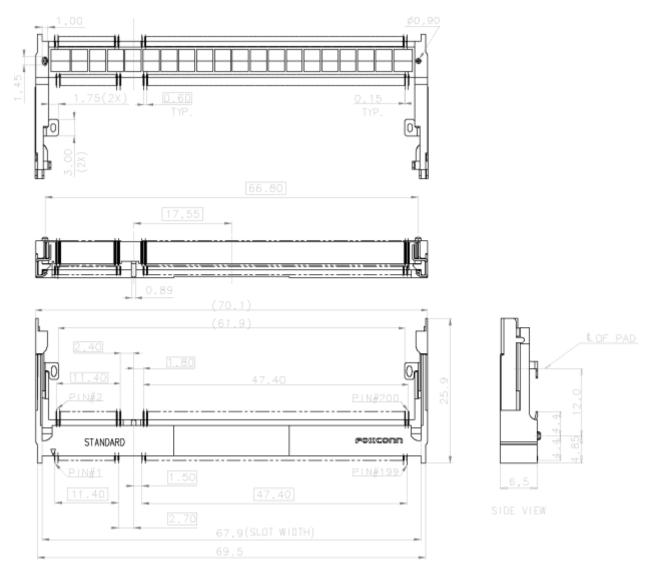

| 12   | Module Connection                                                      |

| 12.1 | Module Connector DDR2 SO-DIMM60                                        |

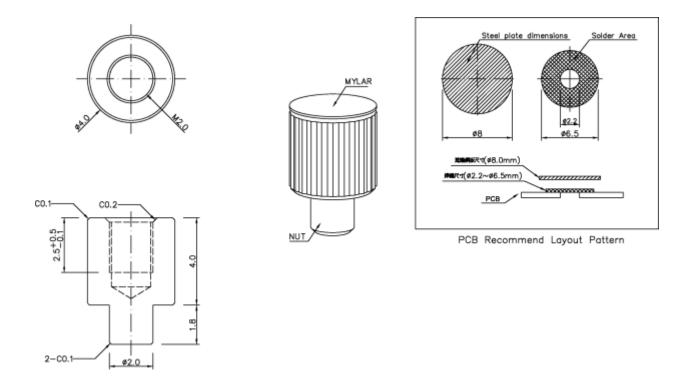

| 12.2 | Nut to Fix TDM-3730 Module to the Baseboard61                          |

| 13   | Disclaimer62                                                           |

| 14   | Warranty                                                               |

#### TDM-3730 HARDWARE MANUAL rev A

March 6 2012, TechNexion

| 15 | Contact Information | 64 |

|----|---------------------|----|

|----|---------------------|----|

## 2 Revision

| Revision | Date       | Description                                | Created by |

|----------|------------|--------------------------------------------|------------|

| 0.90     | 21/06/2011 | Preliminary version                        | TechNexion |

| А        | 05/07/2011 | First public version                       | TechNexion |

| A-01     | 11/08/2011 | Change in Wifi signals description         | TechNexion |

| A-02     | 06/03/2012 | Add Chapter about multiplexing in Software | TechNexion |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

|          |            |                                            |            |

## 3 Care and Maintenance

## 3.1 General

Your device is a product of superior design and craftsmanship and should be treated with care. The following suggestions will help you.

- Keep the device dry. Precipitation, humidity, and all types of liquids or moisture can contain minerals that will corrode electronic circuits. If your device does get wet, allow it to dry completely.

- Do not use or store the device in dusty, dirty areas. Its moving parts and electronic components can be damaged.

- Do not store the device in hot areas. High temperatures can shorten the life of electronic devices, damage batteries, and warp or melt certain plastics.

- Do not store the device in cold areas. When the device returns to its normal temperature, moisture can form inside the device and damage electronic circuit boards.

- Do not attempt to open the device.

- Do not drop, knock, or shake the device. Rough handling can break internal circuit boards and fine mechanics.

- Do not use harsh chemicals, cleaning solvents, or strong detergents to clean the device.

- Do not paint the device. Paint can clog the moving parts and prevent proper operation.

- Unauthorized modifications or attachments could damage the device and may violate regulations governing radio devices.

These suggestions apply equally to your device, battery, charger, or any enhancement. If any device is not working properly, take it to the nearest authorized service facility for service.

## 3.2 Regulatory Information

## Disposal of Waste Equipment by Users in Private Household in the European Union

This symbol on the product or on its packaging indicates that this product must not be disposed of with your other household waste. Instead, it is your responsibility to dispose of your waste equipment by handing it over to a designated collection point for the recycling of waste electrical and electronic equipment. The separate collection and recycling of your waste equipment at the time of disposal will help to conserve natural resources and ensure that it is

recycled in a manner that protects human health and the environment. For more information about where you can drop off your waste equipment for recycling, please contact your local city office, your household waste disposal service or the shop where you purchased the product.

We hereby declare that the product is in compliance with the essential requirements and other relevant provisions of European Directive 1999/5/EC (radio equipment and telecommunications terminal equipment Directive).

# TechNexion Ltd.

17F-1 No. 16 Jian Ba Road Chung Ho City, 23511, Taipei, Taiwan R.O.C. Phone: +886-2-8227 3585 Fax: :+886-2-8227 3590

#### The Compliance of RoHS New Requirement

According to the new requirements in directive 2002/95/EC, DecaBDE is added with specification starting by July 1, 2008 as follows:

Cadmium (Cd) Lead (Pb) Mercury (Hg) Hexavalent Chromium (Cr6) PBB PBDE (include DecaBDE) : Under 100ppm : Under 1000ppm : Under 1000ppm : Under 1000ppm : Under 1000ppm : Under 1000ppm

Please confirm and send back, thanks.

#### **RoHS Compliance Statement**

We aware the change in this directive and our product can meet this new specification as above.

Company Stamp

Page . \_

# Federal Communications Commission (FCC) Unintentional emitter per FCC Part 15

This device has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference in a residential

installation. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instructions, may cause harmful interference to radio or television reception. However, there is no guarantee that interference will not occur in a particular installation. If this equipment does cause interference to radio and television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:

Reorient or relocate the receiving antenna

Increase the separation between the equipment and receiver

Connect the equipment to an outlet on a different circuit from that to which the receiver is connected

• Consult the dealer or an experienced radio/TV technician for help.

**WARNING!** To reduce the possibility of heat-related injuries or of overheating the computer, do not place the computer directly on your lap or obstruct the computer air vents. Use the computer only on a hard, flat surface. Do not allow another hard surface, such as an adjoining optional printer, or a soft surface, such as pillows or rugs or clothing, to block airflow. Also, do not allow the AC

adapter to contact the skin or a soft surface, such as pillows or rugs or clothing, during operation. The computer and the AC adapter comply with the user-accessible surface temperature limits defined by the International Standard for Safety of Information Technology Equipment (IEC 60950).

## 4 **Description**

The TDM-3730 Is a highly integrated System on Module (SOM) containing the TI ARM Cortex A8 DaVinci DM3730 processor, PMIC, Wireless LAN, USB PHY, LAN Controller, Memory and NAND Flash.

The high-performance, digital media processors are based on the enhanced device architecture and are integrated on advanced 45-nm process technology. This architecture is designed to provide best in class ARM and Graphics performance while delivering low power consumption. This balance of performance and power allow the device to support the following example applications:

- Portable Data Terminals

- Navigation

- Auto Infotainment

- Gaming

- Medical Imaging

- Home Automation

- Human Interface

- Industrial Control

- Test and Measurement

- Single board Computers

The device can support numerous HLOS and RTOS solutions including Linux, Android and Windows Embedded CE by TechNexion and/ or third parties.

One can always check our website (<u>www.technexion.com</u>) for additional product detail information, mechanical design files, software programming guides, source code software and custom baseboard creation guideline.

March 6 2012, TechNexion

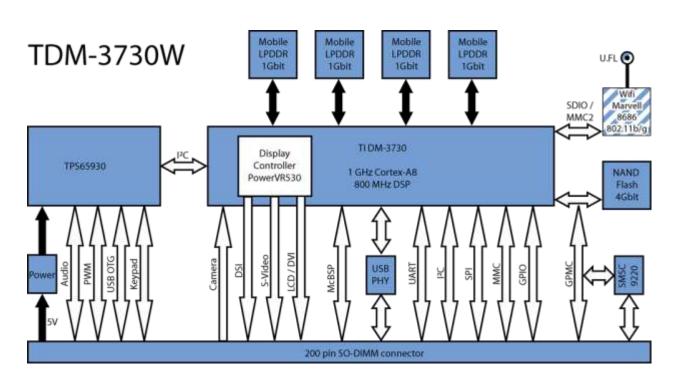

## 4.1 Block Diagram TDM-3730 System on Module

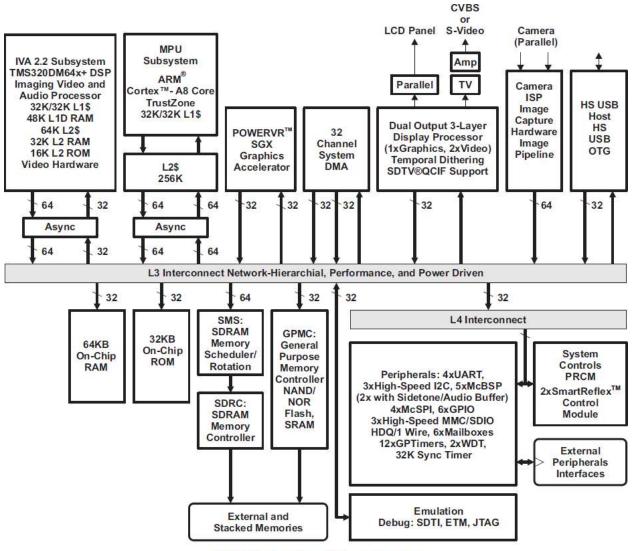

## 4.2 Functional Block Diagram CPU

The functional block diagram of the DM3730 Digital Media Processor is shown below.

DM3730 Functional Block Diagram

## 5 System Components

## 5.1 CPU: DM-3730

#### 5.1.1 DM-3730 Digital Media Processor Features

Texas Instruments (TI) DM3730 Digital Media Processor

- Compatible with OMAP<sup>™</sup> 3 Architecture

- ARM® Microprocessor (MPU) Subsystem

- O Up to 1-GHz ARM® Cortex<sup>™</sup>-A8 Core Also supports 300, 600, and 800-MHz operation

- NEON™ SIMD Coprocessor

- High Performance Image, Video, Audio (IVA2.2TM) Accelerator Subsystem

- Up to 800-MHz TMS320C64x+TM DSP Core Also supports 260, 520, and 660-MHz operation

- Enhanced Direct Memory Access (EDMA) Controller (128 Independent Channels)

- Video Hardware Accelerators

- POWERVR SGX<sup>™</sup> Graphics Accelerator

- Tile Based Architecture Delivering up to 20 MPoly/sec

- Universal Scalable Shader Engine: Multi-threaded Engine Incorporating Pixel and Vertex Shader Functionality

- Industry Standard API Support: OpenGLES 1.1 and 2.0, OpenVG1.0

- Fine Grained Task Switching, Load Balancing, and Power Management

- Programmable High Quality Image Anti-Aliasing

- Advanced Very-Long-Instruction-Word (VLIW) TMS320C64x+TM DSP Core

- Eight Highly Independent Functional Units

- Six ALUs (32-/40-Bit); Each Supports Single 32- bit, Dual 16-bit, or Quad 8-bit, Arithmetic per Clock Cycle

- Two Multipliers Support Four 16 x 16-Bit Multiplies (32-Bit Results) per Clock Cycle or Eight 8 x 8-Bit Multiplies (16-Bit Results) per Clock Cycle

- o Load-Store Architecture With Non-Aligned Support

- 64 32-Bit General-Purpose Registers

- Instruction Packing Reduces Code Size

- All Instructions Conditional

- Additional C64x+TM Enhancements

- Protected Mode Operation

- Expectations Support for Error Detection and Program Redirection

- Hardware Support for Modulo Loop Operation

- C64x+TM L1/L2 Memory Architecture

- 32K-Byte L1P Program RAM/Cache (Direct Mapped)

- o 80K-Byte L1D Data RAM/Cache (2-Way Set- Associative)

- o 64K-Byte L2 Unified Mapped RAM/Cache (4- Way Set-Associative)

- o 32K-Byte L2 Shared SRAM and 16K-Byte L2 ROM

- C64x+TM Instruction Set Features

- Byte-Addressable (8-/16-/32-/64-Bit Data)

- 8-Bit Overflow Protection

- Bit-Field Extract, Set, Clear

- o Normalization, Saturation, Bit-Counting

- Compact 16-Bit Instructions

- Additional Instructions to Support Complex Multiplies

- 1.8-V I/O and 3.0-V (MMC1 only), 0.9-V to 1.2-V Adaptive Processor CoreVoltage

0.9-V to 1.1-V Adaptive Core Logic Voltage

Note: These are default Operating Performance Point (OPP) voltages and could be optimized to lower values using SmartReflex AVS.

- Serial Communication

- Multichannel Buffered Serial Ports (McBSPs)

- 512 Byte Transmit/Receive Buffer (McBSP3)

- 5K-Byte Transmit/Receive Buffer (McBSP2)

- SIDETONE Core Support (McBSP2 and 3 Only) For Filter, Gain, and Mix Operations

- Direct Interface to I2S and PCM Device and T Buses

- 128 Channel Transmit/Receive Mode

- Master/Slave Multichannel Serial Port Interface (McSPI) Ports

- High-Speed/Full-Speed/Low-Speed USB OTG Subsystem (12-/8-Pin ULPI Interface)

- High-Speed/Full-Speed/Low-Speed Multiport USB Host Subsystem

- 12-/8-Pin ULPI Interface or 6-/4-/3-Pin Serial Interface

- One HDQ/1-Wire Interface

- UARTs (One with Infrared Data Association [IrDA] and Consumer Infrared [CIR] Modes)

- Master/Slave High-Speed Inter-Integrated Circuit (I2C) Controllers

- Camera Image Signal Processing (ISP)

- CCD and CMOS Imager Interface

- Memory Data Input

- o BT.601/BT.656 Digital YCbCr 4:2:2 (8-/10-Bit) Interface

- o Glueless Interface to Common Video Decoders

- o Resize Engine

- Resize Images From 1/4x to 4x

- Separate Horizontal/Vertical Control

- System Direct Memory Access (SDMA) Controller (32 Logical Channels With Configurable Priority)

- Comprehensive Power, Reset, and Clock Management

- SmartReflexTM Technology

- Dynamic Voltage and Frequency Scaling (DVFS)

- ARM<sup>®</sup> Cortex<sup>™</sup>-A8 Core

- ARMv7 Architecture

- TrustZone®

- Thumb®-2

- MMU Enhancements

- o In-Order, Dual-Issue, Superscalar Microprocessor Core

- NEON Multimedia Architecture

- Over 2x Performance of ARMv6 SIMD

- Supports Both Integer and Floating Point SIMD

- Jazelle® RCT Execution Environment Architecture

- Dynamic Branch Prediction with Branch Target Address Cache, Global History Buffer, and 8-Entry Return Stack

- Embedded Trace Macrocell (ETM) Support for Non-Invasive Debug

- ARM Cortex-A8 Memory Architecture:

- o 32K-Byte Instruction Cache (4-Way Set-Associative)

- 32K-Byte Data Cache (4-Way Set-Associative)

- o 256K-Byte L2 Cache

- 32K-Byte ROM

- 64K-Byte Shared SRAM

- Endianess:

- ARM Instructions Little Endian

- ARM Data Configurable

- DSP Instructions/Data Little Endian

- Removable Media Interfaces:

- Multimedia Card (MMC)/ Secure Digital (SD) With Secure Data I/O (SDIO)

- Test Interfaces

- o IEEE-1149.1 (JTAG) Boundary-Scan Compatible

- Embedded Trace Macro Interface (ETM)

- Serial Data Transport Interface (SDTI

- Up to 125 General-Purpose I/O (GPIO) Pins (Multiplexed With Other Device Functions)

- 45-nm CMOS Technology

- CPU Package:

- o 423-pin s-PBGA package (CUS Suffix), .65mm Ball Pitch

## 5.2 PMIC: TPS-65930

#### 5.2.1 TPS-65930 – Introduction

The TPS65930 devices are power-management ICs for OMAP<sup>™</sup> and other mobile applications. The devices include power-management, a universal serial bus (USB) high-speed (HS) transceiver, light -emitting diode (LED) drivers, an analog-to-digital converter (ADC), a real-time clock (RTC), and embedded power control (EPC). In addition, the TPS65930 includes a full audio codec with two digital-to-analog converters (DACs) and two ADCs to implement dual voice channels, and a stereo downlink channel that can play all standard audio sample rates through a multiple format inter-integrated sound (I2S<sup>™</sup>)/time division multiplexing (TDM) interface.

These optimized devices support the power and peripheral requirements of the OMAP application processors. The power portion of the devices contains three buck converters, two controllable by a dedicated SmartReflex<sup>™</sup> class-3 interface, multiple low dropout (LDO) regulators, an EPC to manage the power sequencing requirements of OMAP, and an RTC and backup module. The RTC can be powered by a backup battery when the main supply is not present, and the devices include a coin-cell charger to recharge the backup battery as needed.

The USB module provides a HS 2.0 OTG transceiver suitable for direct connection to the OMAP UTMI+ low pin interface (ULPI), with an integrated charge pump and full support for the carkit CEA-936A specification. An ADC is provided for monitoring signals, such as supply voltage, entering the device, and two additional external ADC inputs are provided for system use.

The devices provide driver circuitry to power two LED circuits that can illuminate a panel or provide user indicators. The drivers also provide pulse width modulation (PWM) circuits to control the illumination levels of the LEDs. A keypad interface implements a built-in scanning algorithm to decode hardware-based key presses and reduce software use, with multiple additional general-purpose input/output devices (GPIOs) that can be used as interrupts when configured as inputs.

#### 5.2.2 TPS-65930: Features

The TPS65930 devices offer the following features:

- Audio:

- Differential input main microphones

- Mono auxiliary input

- External predrivers for class D (stereo)

- Automatic level control (ALC)

- Digital and analog mixing

- o 16-bit linear audio stereo DAC (96, 48, 44.1, and 32 kHz and derivatives)

- 16-bit linear audio stereo ADC (48, 44.1, and 32 kHz and derivatives)

- USB:

- USB 2.0 on-the-go (OTG)-compliant HS transceivers

- o 12-bit universal transceiver macro interface ULPI

- USB power supply (5-V charge pump for VBUS)

- Additional Features:

- Keypad Interface (up to  $6 \times 6$ )

- Backup battery charger

## 5.3 Memory

The TDM-3730 has a dual channel 32 bit External Memory Interfaces (EMI) controller.

Each 32 bit wide channel is connected 16 bit wide to two Hynix H5MS1G62AFR MOBILE DDR SDRAM Chips SDRAM\_nCS0 and SDRAM\_nCS1 signals are used to select them.

The standard configuration is organized as 1Gbit (4Bank x 16M x 16bits). Therefore given 4 chips are used a total of 4Gbit or 512MB of memory is available.

Features:

- Mobile DDR SDRAM

- Double data rate architecture: two data transfer per clock cycle

- Mobile DDR SDRAM INTERFACE

- x16 bus width

- Multiplexed Address (Row address and Column address)

- SUPPLY VOLTAGE

- $\circ$  1.8V device: VDD and VDDQ = 1.7V to 1.95V

- MEMORY CELL ARRAY

- 1Gbit (x16 device) = 4Bank x 16Mb x 16 I/O

- DATA STROBE

- x16 device: LDQS and UDQS

- Bidirectional, data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver

- Data and data mask referenced to both edges of DQS

- LOW POWER FEATURES

- PASR (Partial Array Self Refresh)

- AUTO TCSR (Temperature Compensated Self Refresh)

- DS (Drive Strength)

- INPUT CLOCK

- Differential clock inputs (CK, CK)

- Data MASK

- LDM and UDM: Input mask signals for write data

- DM masks write data-in at the both rising and falling edges of the data strobe

- MODE and EXTENDED MODE REGISTER SET and STATUS REGISTER READ

- Keep to the JEDEC Standard regulation (Low Power DDR SDRAM)

- CAS LATENCY

- Programmable CAS latency 2 or 3 supported

- BURST LENGTH

- Programmable burst length 2 / 4 / 8 with both sequential and interleave mode

- AUTO PRECHARGE

- Option for each burst access

- AUTO REFRESH AND SELF REFRESH MODE

- CLOCK STOP MODE

- Keep to the JEDEC Standard regulation

- INITIALIZING THE MOBILE DDR SDRAM

- Occurring at device power up or interruption of device power

## 5.4 NAND Flash

NAND on the TDM-3730 is populated as Micron MT29F4G16ABBDAH4D and connected 16 bit wide to the DM3730 GPMC bus.

The default TDM-3730 supports the chip which provides 512MB of addressable space.

The GPMC\_nCS0 signal is used for it's selection.

Features:

- Open NAND Flash Interface (ONFI) 1.0-compliant

- Single-level cell (SLC) technology

- Organization

- Page size x8: 2112 bytes (2048 + 64 bytes)

- Page size x16: 1056 words (1024 + 32 words)

- Block size: 64 pages (128K + 4K bytes)

- Plane size: 2 planes x 2048 blocks per plane

- Device size: 4Gb: 4096 blocks; 8Gb: 8192 blocks

- Asynchronous I/O performance

- o tRC/tWC: 20ns (3.3V), 25ns (1.8V)

- Array performance

- Read page: 25µs

- Program page: 200µs (TYP: 1.8V, 3.3V)

- Erase block: 700µs (TYP)

- Command set: ONFI NAND Flash Protocol

- Operation status byte provides software method for detecting

- Operation completion

- Pass/fail condition

- Write-protect status

- Ready/Busy# (R/B#) signal provides a hardware method of detecting operation completion

- WP# signal: Write protect entire device

- First block (block address 00h) is valid when shipped from factory with ECC. For minimum required ECC, see Error Management.

- Block 0 requires 1-bit ECC if PROGRAM/ERASE cycles are less than 1000

- RESET (FFh) required as first command after poweron

- Alternate method of device initialization (Nand\_Init) after power up (contact factory)

- Internal data move operations supported within the plane from which data is read

- Quality and reliability

- Data retention: 10 years

- Endurance: 100,000 PROGRAM/ERASE cycles

### 5.5 Network: SMSC LAN9220

The LAN9220 is a full-featured, single-chip 10/100 Ethernet controller designed for embedded applications where performance, flexibility, ease of integration and system cost control are required. The LAN9220 is fully IEEE 802.3 10BASE-T and 802.3u 100BASE-TX compliant, and supports HP Auto-MDIX. The variable voltage I/O signals of the LAN9220 accommodate lower voltage I/O signaling without the need for voltage level shifters.

**Qualified Magnetics** – Magnetics listed under this heading have been tested in order to verify proper operation with the specific device listed with it.

**Suggested magnetic** – Magnetics listed under this heading have *not* been tested in order to verify proper operation with the specific device listed with it. This category of magnetic has been evaluated by the contents of the vendor supplied datasheet and legacy performance only.

| Vendor              |                     |                 | Temp          |

|---------------------|---------------------|-----------------|---------------|

| Qualified Magnetics | 5                   |                 |               |

| UDE                 | RT7-115A1K1A        | Integrated RJ45 | 0° - +70° C   |

| Pulse               | H1102               | 16-pin SOIC     | 0° - +70° C   |

| Halo                | TG110-RP55N5        | 16-pin SOIC     | 0° - +70° C   |

| Halo                | HFJ11-RP26E- L12RL  | Integrated RJ45 | 0° - +70° C   |

| Delta               | RJSE1R5310A         | Integrated RJ45 | 0° - +70° C   |

| Pulse               | HX1188              | 16-pin SOIC     | -40° - +85° C |

| Halo                | TG110-RPE5N5        | 16-pin SOIC     | -40° - +85° C |

| Halo                | HFJ11-RPE26E-L12RL  | Integrated RJ45 | -40° - +85° C |

| TDK                 | TLA-6T717W          | Integrated RJ45 | -40° - +85° C |

| Delta               | LFE8505T            | 16-pin SOIC     | -40° - +85° C |

| Suggested Magneti   | CS                  |                 |               |

| Pulse               | J0011D01B           | Integrated RJ45 | 0° - +70° C   |

| Midcom              | 000-7219-35         | Cardbus         | 0° - +70° C   |

| Bothhand            | TS6121C             | 16-pin SOIC     | 0° - +70° C   |

| Bothhand            | LU1S041X-43         | Integrated RJ45 | 0° - +70° C   |

| Midcom              | 000-7090-37R        | 16-pin SOIC     | -40° - +85° C |

| Midcom              | MIC66211-5171T- LF3 | Integrated RJ45 | -40° - +85° C |

| Elec & Eltek        | 820-M0323R          | 16-pin SOIC     | -40° - +85° C |

## 5.6 USB PHY

The SMSC USB3320 is a Hi-Speed USB 2.0 transceiver that provides a configurable physical layer (PHY) solution and is an excellent macth for a wide variety of products. USB3320 uses the industry standard UTMI+ Low Pin Interface (ULPI) to connect the USB Transceiver to the link. ULPI uses a method of in-band signalling and status byte transfers between the link and transceiver to facilitate a USB session with only 12 pins.

## 5.7 WiFi Module

The Marvell® 88W8686 is a low-power highly-integrated IEEE 802.11g/b MAC/Baseband/RF WLAN system-on-chip (SoC), designed to support IEEE 802.11g payload data rates of 6, 9, 12, 18, 24, 36, 48, and 54 Mbps, as well as 802.11b data rates of 1, 2, 5.5, and 11 Mbps.

General features:

- Ultra low-power dissipation

- Single-chip integration of 802.11g/b wireless RF and baseband, MAC, CPU, memory, and host interfaces

- Integrates all RF to baseband transmit and receive operations, with support for external PAs

- Fully integrated frequency synthesizers with optimized phase noise performance for OFDM applications

- Integrated direct conversion WLAN RF radio

- Supports 19.2, 20, 24, 26, 38.4, and 40 MHz oscillator clock sources

- Software backward compatible with 88W8385 and 88W8015 devices

| SIGNAL NAME | DESCRIPTION            |

|-------------|------------------------|

| MMC2_CLK    | Clock                  |

| MMC2_CMD    | Command                |

| MMC2_d0     | 4 bit data             |

| MMC2_d1     | 4 bit data             |

| MMC2_d2     | 4 bit data             |

| MMC2_d3     | 4 bit data             |

| GPIO54      | Reserved               |

| GPIO 157    | Wifi enable – power on |

#### 5.7.1 WiFi Signals Description

#### 5.7.2 I-PEX Connector

March 6 2012, TechNexion

## 6 How to use the Multiplex Mode

The function of the pins on the module can be changed by adjusting the multiplex mode (mux).

### 6.1 Multiplexing in u-boot (Linux)

Multiplexing can be done in u-boot in the tdm3730.h file

(Use the file in this directory: board/technexion/tdm3730/tdm3730.h)

Example of what it might look like:

#### MUX\_VAL(CP(ETK\_D2), (IEN|PTD|EN|M4))

The last part "M4" is the multiplex mode and you can change that according the table in the Chapter 7.

The line of code is build up as follows:

- The name of the variable is the function in Mode 0; ETK\_D2

- The current Multiplex mode is M4, which means that currently this pin is GPIO\_16

| Pin # | Ball # | Pin Name   | mode | V   | type | description                                      |

|-------|--------|------------|------|-----|------|--------------------------------------------------|

|       |        | MCSPI3 CS0 | 1    |     | Ю    | SPI Enable 0, polarity<br>configured by software |

|       | AC7    | etk_d2     | 0    | 1.8 | 0    | ETK data 2                                       |

| 84    |        | GPIO_16    | 4    |     | 10   | General-purpose IO 16                            |

|       |        | Mm1_txdat  | 5    |     | 10   | USB data. Used as VP in 4-<br>pin VP_VM mode     |

|       |        | Hw_dbg4    | 7    |     | 0    | Debug signal 4                                   |

Table 1: Example of pin 84 on the TDM-3730 module and the different functions for each multiplex mode (see Chapter 7)

#### After this you will need to recompile:

| Uboot# | make distclean      |

|--------|---------------------|

| Uboot# | make tdm3730_config |

| Uboot# | make tdm3730        |

This will create the u-boot.bin

## 6.2 Multiplexing in Windows Embedded Compact 7

Change the following file:

$\label{eq:c:WINCE700} c:\WINCE700\platform\TN_TDM_3730\SRC\INC\bsp_padcfg.h$

March 6 2012, TechNexion

Change code :

#define GPIO\_PADS\_37XX \

PAD\_ENTRY(ETK\_D4, INPUT\_DISABLED | MUXMODE(4)) /\* GPIO 18 \*/ \

Then recompile

| Pin # | Ball # | Pin Name      | mode | V            | type | description                                                       |

|-------|--------|---------------|------|--------------|------|-------------------------------------------------------------------|

| 1     | Х      | VBUS_5V       |      | 5            | 1    | Power                                                             |

| 2     | Х      | DC_5V         |      | 5            | 1    | 5V                                                                |

| 3     | Х      | GND           |      | GND          | GND  | Power                                                             |

| 4     | Х      | DC_5V         |      | 5            | 1    | 5V                                                                |

| 5     | х      | PreDriv.RIGHT |      |              | 0    | Predriver output right P for external class-D amplifier           |

| 6     | Х      | DC_5V         |      | 5            | 1    | 5V                                                                |

| 7     | х      | PreDriv.LEFT  |      |              | 0    | Predriver output left P for<br>external class-D amplifier         |

| 8     | Х      | DC_5V         |      | 5            | 1    | 5V                                                                |

| 9     | х      | MIC_BIAS_G    |      | GND          | GND  | Dedicated ground for<br>microphones                               |

| 10    | Х      | DC_5V         |      | 5            | 1    | 5V                                                                |

| 11    | х      | MIC_MAIN_P    |      | 2.5/<br>2.75 | I    | Main microphone left input (P)                                    |

| 12    | Х      | DC_5V         |      | 5            | 1    | 5V                                                                |

| 13    | x      | PWR_ON        |      | 4.2          | I    | Input; detect a control<br>command to start or stop the<br>system |

| 14    | AA10   | SYS_nRESPWRON | 0    | 1.8          | 1    | Power On Reset                                                    |

| 15    | Х      | HOST nOC      |      | 1.8          | 10   | HOST nOC                                                          |

| 16    | Х      | RESETB        |      |              |      | USB PHY                                                           |

| 17    | Х      | SYSEN         |      | 1.8          | OD   | System enable output                                              |

| 18    | Х      | LEDA          |      | 4.2          | D    | User definable LED Indicator                                      |

| 19    | Х      | GND           |      | GND          | GND  | Power                                                             |

| 20    | Х      | MMC1 CD       |      | 1.8          | IO   | Card Detection1                                                   |

| 21    | Х      | HSUSB ID      |      | 4.2          | 10   | USB ID                                                            |

| 22    | Х      | LCD PWM       |      | 1.8          | IO   | LCD Backlight on/off                                              |

| 23    | Х      | MIC MAIN M    |      | 2.5/<br>2.75 | I    | Main microphone left input<br>(M)                                 |

| 24    | х      | AUXR          |      | 2.5/<br>2.75 | I    | Auxiliary audio input right                                       |

| 25    | х      | MIC BIAS      |      | 2.5/<br>2.75 | Pwr  | Analog microphone bias 1                                          |

| 26    | Х      | CHRG STATE    |      | 1.5          | 10   | Battery type                                                      |

| 27    | Х      | VIO 1V8       |      | 1.8          | 0    | Power                                                             |

| 28    | Х      | DVI_nDISABLE  |      | 1.8          | 10   | DVI/ Backlight control                                            |

| 29    | Х      | VIO 1V8       |      | 1.8          | 0    | Power                                                             |

| 30    | Х      | LCD ENBKL     |      | 1.8          | 10   | LCD Backlight Control                                             |

| 31    | Х      | VIO 1V8       |      | 1.8          | 0    | Power                                                             |

| 32    | Х      | HSUSB DN      |      | 4.2          |      | USB data N/USB carkit<br>transmit data                            |

| 33    | Х      | VIO 1V8       |      | 1.8          | 0    | Power                                                             |

## 7 TDM-3730 Module Pin Description

| Pin #      | Ball # | Pin Name    | mode | V            | type | description                                      |

|------------|--------|-------------|------|--------------|------|--------------------------------------------------|

|            |        |             | mouo |              |      | USB data P/USB carkit                            |

| 34         | X      | HSUSB DP    |      | 4.2          | IO   | receive data                                     |

| 35         | Х      | IDM0        |      |              | IOA  | USB PHY 3320C                                    |

| 36         | x      | ADCIN2      |      | 2.5/<br>2.75 | I    | General –purpose ADC Input                       |

| 37         | Х      | IDP0        |      |              | IOA  | USB PHY 3320C                                    |

| 38         | Х      | CAM IO      |      | 4.2          |      | VBAT.RIGHT - VAUX2.OUT                           |

| 39         | Х      | VMMC1       |      | 4.2          | 0    | Power                                            |

|            |        | MCSPI1 SIMO | 0    |              | 10   | Slave data in, master data out                   |

| 40         | R4     | MMC2_dat5   | 1    | 1.8          | 10   | MMC/SD Card Data bit 5                           |

| 40         | K4     | GPIO_172    | 4    | 1.0          | 10   | General-purpose IO 172                           |

|            |        | Safe_mode   | 7    |              |      |                                                  |

|            |        | MCSPI1 CLK  | 0    |              | 10   | SPI Clock                                        |

| 41         | Т5     | MMC2_dat4   | 1    | 1.8          | 10   | MMC/SD Card Data bit 4                           |

| 41         | 15     | GPIO_171    | 4    | 1.0          | 10   | General-purpose IO 171                           |

|            |        | Safe_mode   | 7    |              |      |                                                  |

| 42         | Х      | KPD.C4      |      | 1.8          | D    | Keypad column 4                                  |

|            |        | MCSPI1 SOMI | 0    |              | 10   | Slave data out, master data in                   |

| 43         | T4     | Mmc2_dat6   | 1    | 1.8          | 10   | MMC/SD Card Data bit 6                           |

| 43         |        | GPIO_173    | 4    |              | 10   | General-purpose IO 173                           |

|            |        | Safe_mode   | 7    |              |      |                                                  |

| 44         | Х      | KPD.C3      |      | 1.8          | D    | Keypad column 3                                  |

|            |        | mcspi1_cs0  | 0    |              | Ю    | SPI Enable 0, polarity<br>configured by software |

| 45         | T6     | Mmc2_dat7   | 1    | 1.8          | 10   | MMC/SD Card Data bit 7                           |

|            |        | GPIO_174    | 4    |              | 10   | General-purpose IO 174                           |

|            |        | Safe_mode   | 7    |              |      |                                                  |

| 46         | Х      | KPD.C2      |      | 1.8          | D    | Keypad column 2                                  |

|            |        | mcbsp3_fsx  | 0    |              | Ю    | Combined frame<br>synchronization                |

| 47         | V4     | Uart2_rx    | 1    | 1.8          | 1    | UART2 Receive data                               |

|            |        | GPIO_143    | 4    |              | 10   | General-purpose IO 143                           |

|            |        | Safe_mode   | 7    |              | -    |                                                  |

| 48         | Х      | KPD.C1      |      | 1.8          | D    | Keypad column 1                                  |

|            |        | Mcbsp3_dr   | 0    |              | 1    | Received serial data                             |

| 40         |        | Uart2_rts   | 1    | 1.0          | 0    | UART2 request to send                            |

| 49         | V5     | GPIO 141    | 4    | 1.8          | 10   | General-purpose IO 141                           |

|            |        | Safe mode   | 7    |              |      |                                                  |

| 50         | Х      | KPD.C0      |      | 1.8          | D    | Keypad column 0                                  |

|            |        | MCBSP3 CLKX | 0    |              | 10   | Combined serial clock                            |

| <b>F</b> 4 | 10/4   | UArt 2_TX   | 1    | 1.0          | 0    | UART2_transmit data                              |

| 51         | W4     | GPIO_142    | 4    | 1.8          | 10   | General-purpose IO 142                           |

|            |        | Safe mode   | 7    | 1            |      |                                                  |

| 52         | Х      | KPD.R4      |      | 1.8          | 1    | Keypad row 4                                     |

| Pin # | Ball # | Pin Name      | mode | V   | type | description                   |

|-------|--------|---------------|------|-----|------|-------------------------------|

|       |        | MCBSP3_DX     | 0    |     | 10   | Transmitted serial data       |

| 50    | V6     | UART2_CTS     | 1    | 10  | 1    | UART2_CTS                     |

| 53    | VO     | GPIO_140      | 4    | 1.8 | Ю    | General-purpose IO 140        |

|       |        | Safe mode     | 7    |     |      |                               |

| 54    | Х      | KPD.R3        |      | 1.8 | 1    | Keypad row 3                  |

|       |        | MCBSP2_CLKX   | 0    |     | 10   | Combined serial Clock         |

| 55    | T21    | GPIO_117      | 4    | 1.8 | Ю    | General-purpose IO 117        |

|       |        | Safe_mode     | 7    |     |      |                               |

| 56    | Х      | KPD.R2        |      | 1.8 | 1    | Keypad row 2                  |

|       |        | Sys_boot 5    | 0    |     | 1    | Boot configuration mode bit 5 |

|       |        | -             |      |     |      | Direction control for DAT4,   |

|       |        | Mmo2 dir dat2 | 1    |     | 0    | DAT5, DAT6, and DAT7          |

| 57    | AB16   | Mmc2_dir_dat3 | I    | 1.8 | 0    | signals case an external      |

| 57    | ADIO   |               |      | 1.0 |      | transceiver used              |

|       |        | Dss_data22    | 3    |     | 0    | LCD Pixel Data bit 22         |

|       |        | GPIO_7        | 4    |     | Ю    | General-purpose IO 7          |

|       |        | Safe_mode     | 7    |     |      |                               |

| 58    | Х      | KPD.R1        |      | 1.8 | 1    | Keypad row 1                  |

|       | R20    | Mcbsp2_dx     | 0    |     | Ю    | Transmitted serial data       |

| 59    |        | GPIO_119      | 4    | 1.8 | Ю    | General-purpose IO 119        |

|       |        | Safe mode     | 7    |     |      |                               |

| 60    | Х      | KPD.R0        |      | 1.8 | 1    | Keypad row 0                  |

|       |        | Mcbsp2_dr     | 0    |     | 10   | Received serial data          |

| 61    | V19    | GPIO_118      | 4    | 1.8 | Ю    | General-purpose IO 118        |

|       |        | Safe mode     | 7    |     |      |                               |

| 62    | Х      | KPD.R5        |      | 1.8 | 1    | Keypad row 5                  |

|       |        | Mohan2 fax    | 0    |     | 10   | Combined frame                |

| 63    | V20    | Mcbsp2_fsx    | 0    | 1.8 | 10   | synchronization               |

| 03    | VZ0    | GPIO_116      | 4    | 1.0 | Ю    | General-purpose IO 116        |

|       |        | Safe mode     | 7    |     |      |                               |

|       |        | LCD PON       | 4    |     | Ю    | General-purpose IO 139        |

|       |        | Mmc2_dat7     | 0    |     | Ю    | MMC/ SD Card Data bit 7       |

| 64    | AA1    | Mmc2_clkin    | 1    | 1.8 | 1    | MMC/ SD Input Clock           |

| 04    | AAT    | Mmc3_dat3     | 3    | 1.0 | Ю    | MMC/ SD Card Data bit 3       |

|       |        | Mm3_rxdm      | 6    |     | Ю    | Transmit enable               |

|       |        | Safe mode     | 7    |     |      |                               |

| Pin # | Ball # | Pin Name          | mode   | V   | type     | description                    |

|-------|--------|-------------------|--------|-----|----------|--------------------------------|

|       |        | LCD INI           | 4      | -   | 10       | General-purpose IO 137         |

|       |        | Mmc2_dat5         | 0      |     | 10       | MMC/SD card data bit 5         |

|       |        |                   |        | -   | 10       | Direction control for DAT1     |

|       |        | Mmc2_dir_dat1     | 1      |     | 0        | and DAT3 signals case an       |

|       |        | Willioz_dil_ddill | •      |     | Ŭ        | external transceiver used      |

| 65    | AA2    |                   |        | 1.8 |          | Global reset is used strobe    |

| 00    | 70.2   | Cam_global_reset  | 2      | 1.0 | IO       | synchronization                |

|       |        | Mmc3_dat1         | 3      | -   | 10       | MMC/SD Card Data bit 1         |

|       |        |                   |        | -   |          | Vplus receive data (not used   |

|       |        | Mm3_rxdp          | 6      |     | Ю        | in 3- or 4-pin configurations) |

|       |        | Safe mode         | 7      |     | -        |                                |

|       |        | LCD envdd         | 4      |     | 10       | General-purpose IO 138         |

|       |        | Mmc2 dat6         | 0      |     | 10       | MMC/SD Card Data bit 6         |

|       |        |                   |        |     |          | Direction control for CMD      |

|       |        | Mmc2 dir cmd      | 1      |     | 0        | signal case an external        |

| 66    | Y2     |                   |        | 1.8 | -        | transceiver is used            |

|       |        | Care abuttan      | 0      | -   | <u> </u> | Mechanical shutter control     |

|       |        | Cam_shutter       | 2      |     | 0        | signal                         |

|       |        | Mmc3_dat2         | 3      |     | 10       | MMC/SD Card Data bit 2         |

|       |        | Safe mode         | 7      |     |          |                                |

|       |        | TS nPEN IRQ       | 4      | 1.8 | 10       | General-purpose IO 136         |

|       |        | Mmc2_dat4         | 0      |     | 10       | MMC/SD Card Data bit 4         |

|       |        | Mmc2_dir_dat0     |        |     |          | Direction control for DAT2     |

| 67    | AB2    |                   | 1      |     | 0        | signal case an external        |

| 07    |        |                   |        |     |          | transceiver used               |

|       |        | Mmc3_dat0         | 3      |     | ю        | MMC/SD Card Data bit 0 /       |

|       |        |                   |        |     |          | SPI Serial Input               |

|       |        | Safe mode         | 7      |     | 10       |                                |

|       |        | GPIO_12           | 4      |     | 10       | General-purpose IO 12          |

|       |        | etk_clk           | 0      | _   | 0        | ETK trace clock                |

|       |        | mcbsp5_ clkx      | 1      |     | 10       | Combined serial clock          |

| 68    | AC1    | mmc3_clk          | 2      | 1.8 | 0        | MMC/SD Output Clock            |

|       |        | mm1_rxdp          | 5      |     | IO       | Vplus receive data (not used   |

|       |        | huu dhaQ          | 7      | -   | 0        | in 3- or 4-pin configurations) |

|       |        | hw_dbg0           | 7<br>4 |     | 0        | Debug signal 0                 |

|       |        | GPIO_19           | 0      | -   | 10<br>0  | General-purpose IO 19          |

|       |        | _etk_d5           | 0      | _   | 0        | ETK data 5<br>Combined frame   |

| 69    | AD2    | mcbsp5_fsx        | 1      | 1.8 | IO       | synchronization                |

|       |        | mmc3_dat1         | 2      | -   | 10       | MMC/SD Card Data bit 1         |

|       |        | hw_dbg7           | 7      | -   | 0        | Debug signal 7                 |

| 70    | X      | GND               | /      | GND | GND      | Ground                         |

| 10    | ~      | Sys_clkout1       | 0      |     | 0        | Configurable output clock1     |

| 71    | Y7     | GPIO 10           | 4      | 1.8 | 10       | General-purpose IO 10          |

|       |        | Safe_mode         | 7      | 1   |          |                                |

|       |        |                   | 1      |     |          |                                |

| Pin #      | Ball # | Pin Name      | mode | V   | type | description                                                    |

|------------|--------|---------------|------|-----|------|----------------------------------------------------------------|

|            |        | GPIO_13       | 4    |     | 10   | General-purpose IO 13                                          |

| 72         | 102    | etk_ctl       | 0    | 10  | 0    | ETK trace ctl                                                  |

| 12         | AD3    | mmc3_cmd      | 2    | 1.8 | 10   | MMC/SD command signal                                          |

|            |        | hw_dbg1       | 7    |     | 0    | Debug signal 1                                                 |

|            |        | I2C3_sda      | 0    |     | IOD  | I2C Serial Bidirectional Data.                                 |

| 73         | AC12   |               |      | 1.8 |      | Output is open drain.                                          |

| 75         | ACIZ   | GPIO_185      | 4    | 1.0 | 10   | General-purpose IO 185                                         |

|            |        | Safe mode     | 7    |     |      |                                                                |

|            |        | GPIO_18       | 4    |     | 10   | General-purpose IO 18                                          |

|            |        | Etk_d4        | 0    | _   | 0    | ETK data 4                                                     |

| 74         | AC5    | Mcbsp5_dr     | 1    | 1.8 | 1    | Received serial data                                           |

| <i>,</i> , | 100    | Mmc3_dat0     | 2    | 1.0 | Ю    | MMC/SD Card Data bit 0 /<br>SPI Serial Input                   |

|            |        | Hw_dbg6       | 7    |     | 0    | Debug signal 6                                                 |

|            |        | I2C3 SCL      | 0    |     | OD   | I2C Master Serial clock.                                       |

| 75         | AC13   | 1203 30L      | 0    | 1.8 | 00   | Output is open drain                                           |

| 75         | ACIS   | GPIO_184      | 4    | 1.0 | 10   | General-purpose IO 184                                         |

|            |        | safemode      | 7    |     |      |                                                                |

| 70         | AC14   | I2C2 SDA      | 0    | 1.0 | IOD  | I2C Serial Bidirectional Data.<br>Output is open drain.        |

| 76         |        | GPIO_183      | 4    | 1.8 | 10   | General-purpose IO 183                                         |

|            |        | Safe_mode     | 7    |     |      |                                                                |

|            |        | MCSPI3 SIMO   | 1    |     | ю    | Slave data in, master data out<br>IO                           |

|            |        | Etk_d0        | 0    |     | 0    | ATK data 0                                                     |

| 77         | AD6    | Mmc3_dat4     | 2    | 1.8 | 10   | MMC/SD Card Data bit 4                                         |

| 11         | ADO    | GPIO_14       | 4    | 1.0 | 10   | General-purpose IO 14                                          |

|            |        | Mm1_rxcv      | 5    |     | ю    | Differential receiver signal<br>input (not used in 3-pin mode) |

|            |        | Hw_dbg2       | 7    | -   | 0    | Debug signal 2                                                 |

|            |        | I2C2 SCL      | 0    |     | OD   | I2C Master Serial clock.<br>Output is open drain               |

| 78         | AC15   | GPIO_168      | 4    | 1.8 | 10   | General-purpose IO 168                                         |

|            |        | <br>Safe_mode | 7    |     |      |                                                                |

| 79         | Х      | GND           |      | GND | GND  | Ground                                                         |

|            |        | MCSPI3 SOMI   | 1    |     | 10   | Slave data out, master data in                                 |

|            |        | Etk_d1        | 0    |     | 0    | ETK data 1                                                     |

| 80         | 100    | GPIO_15       | 4    | 1.8 | 10   | General-purpose IO 15                                          |

| 80         | AC6    | <br>Mm1_txse0 | 5    |     | ю    | Single-ended zero. Used as VM in 4-pin VP_VM mode.             |

|            |        | Hw_dbg3       | 7    | 1   | 0    | Debug signal 3                                                 |

| Pin # | Ball # | Pin Name              | mode | V   | type | description                                      |

|-------|--------|-----------------------|------|-----|------|--------------------------------------------------|

|       |        |                       |      |     |      | SPI Enable 1, polarity                           |

|       |        | MCSPI3_CS1            | 1    |     | 0    | configured by software                           |

|       |        | etk_d7                | 0    |     | 0    | ETK data 7                                       |

| 81    | AD9    | mmc3_dat7             | 2    | 1.8 | Ю    | MMC/SD Card Data bit 7                           |

|       |        | GPIO_21               | 4    |     | Ю    | General-purpose IO 21                            |

|       |        | mm1_txen_n            | 5    |     | Ю    | Transmit enable                                  |

|       |        | hw_dbg9               | 7    |     | 0    | Debug signal 9                                   |

|       |        | MCSPI3 CLK            | 1    |     | Ю    | SPI Clock                                        |

|       |        | Etk_d3                | 0    |     | 0    | ETK data 3                                       |

| 82    | AD8    | Mmc3_dat3             | 2    | 1.8 | Ю    | MMC/SD Card Data bit 3                           |

|       |        | GPIO_17               | 4    |     | IO   | General-purpose IO 17                            |

|       |        | Hw_dbg5               | 7    |     | 0    | Debug signal 5                                   |

| 83    | AB24   | TV SVIDEO Y           | 0    | 1.8 | AO   | TV analog output Composite:<br>cvideo1_out       |

|       |        | MCSPI3 CS0            | 1    |     | Ю    | SPI Enable 0, polarity<br>configured by software |

|       |        | etk_d2                | 0    |     | 0    | ETK data 2                                       |

| 84    | AC7    | GPIO_16               | 4    | 1.8 | Ю    | General-purpose IO 16                            |

|       |        | Mm1_txdat             | 5    |     | Ю    | USB data. Used as VP in 4-<br>pin VP_VM mode     |

|       |        | Hw_dbg4               | 7    |     | 0    | Debug signal 4                                   |

| 85    | AA23   | TV SVIDEO C           | 0    | 1.8 | AO   | TV analog output S-VIDEO:<br>cvideo2_out         |

|       |        | UART1 CTS             | 0    | 1.8 | 1    | UART1 Clear To Send                              |

| 86    | AC2    | GPIO_150              | 4    |     | Ю    | General-purpose IO 150                           |

|       |        | Safe_mode             | 7    |     |      |                                                  |

|       |        | UART1 RTS             | 0    |     | 0    | UART1 Request To Send                            |

| 87    | W6     | GPIO_149              | 4    | 1.8 | Ю    | General-purpose IO 149                           |

|       |        | Safe_mode             | 7    |     |      |                                                  |

|       |        | Mmc1_WP               | 4    | -   | 10   | General-purpose IO 23                            |

|       |        | Etk_d9                | 0    | 4   | 0    | ETK data 9                                       |

| 00    | 4.5.5  | Mmc3_dat5             | 2    | 1.0 | 10   | MMC/SD Card Data bit 5                           |

| 88    | AD5    | Mar 4 minutes         | -    | 1.8 |      | Vminus receive data (not                         |

|       |        | Mm1_rxdm              | 5    |     | IO   | used in 3- or 4-pin                              |

|       |        | Lhu dhatt             | 7    | -   | 0    | configurations)                                  |

|       |        | Hw_dbg11              |      |     | 0    | Debug signal 11                                  |

| 80    | W7     | UART1 TX              | 0    | 10  | 0    | UART1 Transmit data<br>General-purpose IO 148    |

| 89    | VV /   | GPIO_148<br>Safe_mode | 4    | 1.8 |      |                                                  |

|       |        | GPIO 20               | 4    |     | IO   | General-purpose IO 20                            |

|       |        | Etk_d6                | 0    | -   | 0    | ETK data 6                                       |

|       |        |                       |      | -   |      | Transmitted serial data O                        |

| 90    | AC8    | Mcbsp5_dx             | 1    | 1.8 | 0    | AF13                                             |

|       |        | Mmc3_dat2             | 2    |     | 10   | MMC/SD Card Data bit 2                           |

| 01    | V      | Hw_dbg8               | 7    | 1.0 | 0    | Debug signal 8                                   |

| 91    | Х      | KPD.C5                |      | 1.8 | D    | Keypad column 5                                  |

| Pin # | Ball # | Pin Name     | mode | V    | type     | description                    |

|-------|--------|--------------|------|------|----------|--------------------------------|

|       |        | UART1 RX     | 0    | -    |          | UART1 Receive data             |

|       |        | Mcbsp1 clkr  | 2    | -    | 10       | Receive Clock                  |

| 92    | V7     | Mcspi4_clk   | 3    | 1.8  | 10       | SPI Clock                      |

|       |        | GPIO 151     | 4    | 1    | 10       | General-purpose IO 151         |

|       |        | Safe mode    | 7    | -    |          |                                |

|       |        | MMC1 DAT3    | 0    |      | 10       | MMC/SD Card Data bit 3         |

| 93    | N23    | GPIO125 (2)  | 4    | 1.8/ | 10       | General-purpose IO 125         |

| 00    | 1120   | Safe mode    | 7    | 3.3  | 10       |                                |

|       |        | MMC1 DAT2    | 0    |      | 10       | MMC/SD Card Data bit 2         |

| 94    | M20    | GPIO_124 (2) | 4    | 1.8/ | 10       | General-purpose IO 124         |

| 01    | 11120  | Safe mode    | 7    | 3.3  |          |                                |

|       |        | MMC1 CLK0    | 0    |      | 0        | MMC/SD Output Clock            |

| 95    | M23    | GPIO_120 (2) | 4    | 1.8/ | 10       | General-purpose IO 120         |

| 00    | 11120  | Safe mode    | 7    | 3.3  |          |                                |

|       |        | MMC1 DAT1    | 0    |      | 10       | MMC/SD Card Data bit 1         |

| 96    | M21    | GPIO_123 (2) | 4    | 1.8/ | 10       | General-purpose IO 123         |

| 50    |        | Safe mode    | 7    | 3.3  |          |                                |

|       |        |              |      |      |          | MMC/SD Card Data bit 0/ SPI    |

|       |        | MMC1 DAT0    | 0    | 1.8/ | Ю        | Serial Input                   |

| 97    | M22    | GPIO_122 (2) | 4    | 3.3  | 10       | General-purpose IO 122         |

|       |        | Safe_mode    | 7    |      |          |                                |

|       |        | DSS D21      | 0    |      | 0        | LCD Pixel Data bit 21          |

|       | K22    |              |      | 1.8  |          | SPI Enable 0, polarity         |

|       |        | Mcspi3_cs0   | 2    |      | Ю        | configured by software         |

| 98    |        | Dss data3    | 3    |      | 10       | LCD Pixel Data bit 3           |

|       |        | GPIO_91      | 4    |      | 10       | General-purpose IO 91          |

|       |        | Safe_mode    | 7    |      |          |                                |

|       |        | MMC1 CMD     | 0    |      | 10       | MMC/SD command signal          |

| 99    | L23    | GPIO_121 (2) | 4    | 1.8/ | 10       | General-purpose IO 121         |

|       |        | Safe_mode    | 7    | 3.3  |          |                                |

|       |        |              |      |      | <u> </u> | AC bias control (STN) or pixel |

| 400   | 10.4   | DSS ACBIAS   | 0    |      | 0        | data enable (TFT) output       |

| 100   | J21    | GPIO_69      | 4    | 1.8  | 10       | General-purpose IO 69          |

|       |        | Safe_mode    | 7    | 1    |          |                                |

|       |        | DSS D16      | 0    |      | 10       | LCD Pixel Data bit 16          |

| 101   | J22    | GPIO_86      | 4    | 1.8  | 10       | General-purpose IO 86          |

|       |        | Safe_mode    | 7    |      |          |                                |

|       |        | DSS D10      | 0    |      | IO       | LCD Pixel Data bit 10          |

| 102   | AC22   | GPIO_80      | 4    | 1.8  | Ю        | General-purpose IO 80          |

|       |        | Safe_mode    | 7    |      |          |                                |

|       |        | Dss_data19   | 0    |      | IO       | LCD Pixel Data bit 19          |

|       |        | mcspi3_simo  | 2    | 1    | Ю        | Slave data in, master data out |

| 103   | H23    | dss_data1    | 3    | 1.8  | Ю        | LCD Pixel Data bit 1           |

| 100   |        | GPIO_89      | 4    | 1    | 10       | General-purpose IO 89          |

|       |        | 0110_00      | •    |      |          |                                |

| Pin # | Ball # | Pin Name      | mode | V          | type | description                          |

|-------|--------|---------------|------|------------|------|--------------------------------------|

|       |        | Dss data11    | 0    |            | 10   | LCD Pixel Data bit 11                |

| 104   | AC23   | GPIO_81       | 4    | 1.8        | 10   | General-purpose IO 81                |

| -     |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss data18    | 0    |            | 10   | LCD Pixel Data bit 18                |

|       |        | mcspi3_clk    | 2    |            | Ю    | SPI Clock                            |

| 105   | G24    | dss_data0     | 3    | 1.8        | Ю    | LCD Pixel Data bit 0                 |

|       |        | GPIO_88       | 4    |            | IO   | General-purpose IO 88                |

|       |        | safe_mode     | 7    |            |      |                                      |

|       |        | Dss_data4     | 0    |            | 10   | LCD Pixel data bit 4                 |

| 106   | AD21   | Uart3_rx_irrx | 2    | 1.8        | I    | UART3 Receive data, IR and Remote RX |

|       |        | GPIO_74       | 4    | 1          | 10   | General-purpose IO 74                |

|       |        | Safe mode     | 7    | 1          |      |                                      |

|       |        | Dss_data17    | 0    |            | 10   | LCD Pixel data bit 17                |

| 107   | G23    | GPIO_87       | 4    | 1.8        | Ю    | General-purpose IO 87                |

|       |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss_data12    | 0    |            | 10   | LCD Pixel data bit 12                |

| 108   | AB22   | GPIO_82       | 4    | 1.8        | 10   | General-purpose IO 82                |

|       |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss_pclk      | 0    | 1.8 0<br>0 | 0    | LCD Pixel Clock                      |

| 109   | G22    | GPIO_66       | 4    |            | Ю    | General-purpose IO 66                |

| 109   | 622    | Hw_dbg12      | 5    |            | 0    | Debug signal 12                      |

|       |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss_data5     | 0    |            | Ю    | LCD Pixel data bit 5                 |

| 110   | AC21   | Uart3_tx_irtx | 2    | 1.8        | 0    | UART3 Transmit data, IR TX           |

| 110   | ACZI   | GPIO_75       | 4    | 1.0        | IO   | General-purpose IO 75                |

|       |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss_data9     | 0    |            | Ю    | LCD Pixel data bit 8                 |

|       |        | Uart3_tx_irtx | 2    |            | 0    | UART3 Transmit data, IR TX           |

| 111   | F23    | GPIO_79       | 4    | 1.8        | Ю    | General-purpose IO 79                |

|       |        | Hw_dbg17      | 5    |            | 0    | Debug signal 17                      |

|       |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss_data0     | 0    |            | IO   | LCD Pixel Data bit 0                 |

| 112   | AC19   | Uart1_cts     | 2    | 1.8        | 1    | UART1 Clear To Send                  |

| 112   | 7013   | GPIO_70       | 4    | 1.0        | IO   | General-purpose IO 70                |

|       |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss_vsync     | 0    |            | 0    | LCD Vertical Synchronization         |

| 113   | F22    | GPIO_68       | 4    | 1.8        | Ю    | General-purpose IO 68                |

|       |        | Safe mode     | 7    |            |      |                                      |

|       |        | Dss_data2     | 0    |            | IO   | LCD Pixel Data bit 2                 |

| 114   | AD20   | GPIO_72       | 4    | 1.8        | IO   | General-purpose IO 72                |

|       |        | Safe mode     | 7    |            |      |                                      |

| Pin #   | Ball #   | Pin Name      | mode | V   | type     | description                       |

|---------|----------|---------------|------|-----|----------|-----------------------------------|

| • ••• • | Dan #    | Dss data8     | 0    | •   | 10       | LCD Pixel Data bit 8              |

|         |          | Uart3_rx_irrx | 2    |     | 10       | UART3 Transmit data, IR TX        |

| 115     | E24      | GPIO 78       | 4    | 1.8 | 10       | General-purpose IO 78             |

|         |          | Hw_dbg16      | 5    |     | 0        | Debug signal 16                   |

|         |          | Safe Mode     | 7    | -   | <u> </u> |                                   |

|         |          | Dss_data3     | 0    |     | 10       | LCD Pixel Data bit 3              |

| 116     | AC20     | GPIO_73       | 4    | 1.8 | 10       | General-purpose IO 73             |

|         | /.020    | Safe mode     | 7    |     |          |                                   |

|         |          | Dss_data7     | 0    |     | 10       | LCD Pixel Data bit 7              |

|         |          | Uart1 rx      | 2    |     | ī        | UART1 Receive data                |

| 117     | E23      | GPIO 77       | 4    | 1.8 | IO       | General-purpose IO 77             |

|         |          | Hw_dbg15      | 5    |     | 0        | Debug signal 15                   |

|         |          | Safe_mode     | 7    | -   | -        |                                   |

|         |          | Dss-d1        | 0    |     | IO       | LCD Pixel Data bit 11             |

|         |          | Uart1 rts     | 2    | 1   | 0        | UART1 Request To Send             |

| 118     | AB19     | GPIO_71       | 4    | 1.8 | 10       | General-purpose IO 71             |

|         |          | Safe_mode     | 7    | -   |          |                                   |

|         |          | Dss_data6     | 0    |     | 10       | LCD Pixel Data bit 6              |

|         |          | Uart1_rx      | 2    |     | 1        | UART1 Receive data                |

| 119     | D24      | GPIO76        | 4    | 1.8 | 10       | General-purpose IO 76             |

|         |          | Hw_dbg14      | 5    |     | 0        | Debug signal 14                   |

|         |          | Safe mode     | 7    |     | -        |                                   |

|         |          | Dss_data13    | 0    |     | IO       | LCD Pixel Data bit 13             |

| 120     | Y22      | GPIO 83       | 4    | 1.8 | 10       | General-purpose IO 83             |

| -       |          | Safe mode     | 7    |     |          |                                   |

|         |          | Dss_data20    | 0    |     | 0        | LCD Pixel Data bit 20             |

|         |          | Mcspi3_somi   | 2    |     | 10       | Slave data out, master data in    |

| 121     | D23      | Dss_data3     | 3    | 1.8 | 10       | LCD Pixel Data bit 3              |

|         | _        | GPIO 91       | 4    |     | 10       | General-purpose IO 91             |

|         |          | Safe mode     | 7    | -   |          |                                   |

|         |          | Dss_data14    | 0    |     | 10       | LCD Pixel Data bit 14             |

| 122     | W22      | GPIO_84       | 4    | 1.8 | 10       | General-purpose IO 84             |

|         |          | Safe_mode     | 7    | 1   |          |                                   |

|         |          | <br>Dss_hsync | 0    |     | 0        | LCD Horizontal<br>Synchronization |

| 123     | E22      | GPIO 67       | 4    | 1.8 | 10       | General-purpose IO 67             |

| 125     |          | Hw_dbg13      | 5    | 1.0 | 0        | Debug signal 13                   |

|         |          | Safe_mode     | 7    | 1   |          |                                   |

|         |          | Dss_data23    | 0    |     | 0        | LCD Pixel Data bit 23             |

|         |          | Dss_data5     | 3    | 1   | 10       | LCD Pixel Data bit 5              |

| 124     | W21      | GPIO 93       | 4    | 1.8 | 10       | General-purpose IO 93             |

|         |          | Safe_mode     | 7    | 1   |          |                                   |

| 125     | X        | GND           | -    | GND | GND      | Ground                            |

| 120     | <b>N</b> |               |      |     |          | Ciouna                            |

| Pin # | Ball #      | Pin Name      | mode | V   | type | description                                                                                                     |

|-------|-------------|---------------|------|-----|------|-----------------------------------------------------------------------------------------------------------------|

|       | 2011 //     | Dss data22    | 0    | -   | 0    | LCD Pixel Data bit 22                                                                                           |

|       |             |               |      |     |      | SPI Enable 1, polarity                                                                                          |

|       |             | Mcspi3_cs1    | 2    |     | 0    | configured by software                                                                                          |

| 126   | V21         | Dss_data4     | 3    | 1.8 | 10   | LCD Pixel Data bit 4                                                                                            |

|       |             | GPIO_92       | 4    |     | 10   | General-purpose IO 92                                                                                           |

|       |             | Safe_mode     | 7    |     |      |                                                                                                                 |

|       |             | UART3 TX      | 0    |     | 0    | UART3 Transmit data, IR TX                                                                                      |

| 127   | C23         | GPIO_166      | 4    | 1.8 | 10   | General-purpose IO 166                                                                                          |

|       |             | Safe_mode     | 7    |     |      |                                                                                                                 |

|       |             | Dss_data15    | 0    |     | 10   | LCD Pixel Data bit 15                                                                                           |

| 128   | V22         | GPIO_85       | 4    | 1.8 | 10   | General-purpose IO 85                                                                                           |

|       |             | Safe_mode     | 7    |     |      |                                                                                                                 |

| 100   | D04         | UART3_RX_IRRX | 0    | 1.0 | I    | UART3 Receive data, IR and<br>Remote RX                                                                         |