**USER MANUAL**

COMe-8X90

Computer-On-Module Express

#### Copyright

Copyright © 2012-2013 VIA Technologies Incorporated. All rights reserved.

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise without the prior written permission of VIA Technologies, Incorporated.

#### Trademarks

All trademarks are the property of their respective holders.

#### Disclaimer

No license is granted, implied or otherwise, under any patent or patent rights of VIA Technologies. VIA Technologies makes no warranties, implied or otherwise, in regard to this document and to the products described in this document. The information provided in this document is believed to be accurate and reliable as of the publication date of this document. However, VIA Technologies assumes no responsibility for the use or misuse of the information in this document and for any patent infringements that may arise from the use of this document. The information and product specifications within this document are subject to change at any time, without notice and without obligation to notify any person of such change.

VIA Technologies, Inc. reserves the right the make changes to the products described in this manual at any time without prior notice

#### Regulatory Compliance

#### FCC-A Radio Frequency Interference Statement

This equipment has been tested and found to comply with the limits for a class A digital device, pursuant to part 15 of the FCC rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his personal expense.

#### Notice

The changes or modifications not expressly approved by the party responsible for compliance could void the user's authority to operate the equipment.

#### Notice 2

Shielded interface cables and A.C. power cord, if any, must be used in order to comply with the emission limits.

from overheating

# Battery Recycling and Disposal Only use the appropriate battery specified for this product. Do not re-use, recharge, or reheat an old battery. Do not attempt to force open the battery. ☐ Do not discard used batteries with regular trash. ☐ Discard used batteries according to local regulations. Safety Precautions ☐ Always read the safety instructions carefully. ☐ Keep this User's Manual for future reference. ☐ All cautions and warnings on the equipment should be noted. ☐ Keep this equipment away from humidity. ☐ Lay this equipment on a reliable flat surface before setting it up. Make sure the voltage of the power source and adjust properly 110/220V before connecting the equipment to the power inlet. Place the power cord in such a way that people cannot step on it. Always unplug the power cord before inserting any add-on card or module. ☐ If any of the following situations arises, get the equipment checked by authorized service personnel: • The power cord or plug is damaged. • Liquid has penetrated into the equipment. • The equipment has been exposed to moisture. • The equipment has not worked well or you cannot get it work according to User's Manual. • The equipment has dropped and damaged. • The equipment has obvious sign of breakage. Do not leave this equipment in an environment unconditioned or in a storage temperature above 60°C (140°F). The equipment may be damaged. Do not leave this equipment in direct sunlight. Never pour any liquid into the opening. Liquid can cause damage or electrical shock. Do not place anything over the power cord. Do not cover the ventilation holes. The openings on the enclosure protect the equipment

# **Box Contents**

| CO | Me-8X90                                              |

|----|------------------------------------------------------|

|    | 1 X COMe-8X90 COM Express Module Board               |

|    | 1 x Screw Bag                                        |

|    | 1 x Heatsink or Heatspreader (optional)              |

| CO | Me-8X90 Starter Kit                                  |

|    | 1 x COMe-8X90 COM Express Module Board with Heatsink |

|    | 1 x COMEDB2 COM Express Carrier Board                |

|    | 1 x SATA Cable                                       |

|    | 1 x Dual-Port USB 2.0 Cable                          |

|    | 1 x COM Cable                                        |

|    | 1 x LPT Cable                                        |

|    | 1 x Quick Guide                                      |

|    | 1 x Driver CD                                        |

|    | 1 x LVDS Cable (optional)                            |

|    | 1 x Inverter Cable (optional)                        |

| П  | 1 x 12 1" I CM (optional)                            |

# Table of Contents

| 1. | Produ            | ct Overview                                             | 1  |

|----|------------------|---------------------------------------------------------|----|

|    | 1.1.             | Key Components                                          | 1  |

|    | 1.1.1.           | VIA Nano X2 Processor                                   | 1  |

|    | 1.1.2.           | VIA VX900 System Chipset                                | 2  |

|    | 1.2.             | Product Specifications                                  | 3  |

|    | 1.3.             | Layout Diagram                                          | 6  |

| 2. | Hardv            | vare Installation                                       | 7  |

|    | 2.1.             | CPU                                                     | 7  |

|    | 2.1.1.           | CPU Fan Connector: CPUFAN                               | 8  |

|    | 2.2.             | Memory Module Installation                              | 9  |

|    | 2.2.1.           | Memory Socket: SODIMM                                   | 9  |

|    | 2.2.2.           | Installing the Memory                                   | 10 |

|    | 2.2.3.           | Removing a Memory Module                                | 12 |

|    | 2.3.             | Installing Heatsink with fan/Heatspreader on COMe-8X90  | 13 |

|    | 2.4.             | Mounting COMe-8X90 COM Express to Reference Carrier Boa | rd |

|    | (COME            | DB2)                                                    | 15 |

| 2  | BIOS             | Setup Utility                                           | 2: |

| Э. | 3.1.             | Entering the BIOS Setup Utility                         |    |

|    | 3.2.             | Control Keys                                            |    |

|    | 3.3.             | Navigating the BIOS Menus                               |    |

|    | 3.4.             | Getting Help                                            |    |

|    | 3.5.             | System Overview                                         |    |

|    | 3.5.1.           | AMIBIOS                                                 |    |

|    | 3.5.2.           | Processor                                               |    |

|    | 3.5.3.           |                                                         |    |

|    | 3.5.3.<br>3.5.4. | System Memory                                           |    |

|    | 3.5.5.           | System Date                                             |    |

|    | 3.5.5.           | Advanced Settings                                       |    |

|    | J.U.             | Auvanceu Jeunnys                                        | ∠C |

| 3.6   | .1.         | CPU Configuration                    | 27 |

|-------|-------------|--------------------------------------|----|

| 3.6   | .2.         | IDE Configuration                    | 28 |

| 3.6   | .3.         | Super IO Configuration               | 29 |

| 3.6   | .4.         | Hardware Health Configuration        | 31 |

| 3.6   | .5.         | ACPI Configuration                   | 32 |

| 3.6   | .6.         | APM Configuration                    | 34 |

| 3.6   | .7.         | Spread Spectrum Configuration        | 37 |

| 3.6   | .8.         | USB Configuration                    | 38 |

| 3.6   | .9.         | CRB Configuration                    | 40 |

| 3.7.  | Р           | CI/PnP Settings                      | 41 |

| 3.7   | '.1.        | Clear NVRAM                          | 41 |

| 3.7   | '.2.        | Plug & Play O/S                      | 41 |

| 3.7   | '.3.        | PCI Latency Timer                    | 42 |

| 3.7   | <b>.</b> 4. | Allocate IRQ to PCI VGA              | 42 |

| 3.7   | .5.         | Palette Snooping                     | 42 |

| 3.7   | .6.         | PCI IDE BusMaster                    | 42 |

| 3.7   | .7.         | OffBoard PCI/ISA IDE Card            | 43 |

| 3.7   | .8.         | IRQ3~15                              | 43 |

| 3.7   | '.9.        | DMA Channel 0~7                      | 43 |

| 3.7   | .10.        | Reserved Memory Size                 | 43 |

| 3.7   | 1.11.       | HotPlug Reserve I/O Port Size        | 43 |

| 3.7   | .12.        | HotPlug Reserve Memory Size          | 44 |

| 3.7   | .13.        | HotPlug Reserve PFMemory Size        | 44 |

| 3.8.  | В           | oot Settings                         | 45 |

| 3.8   | 3.1.        | Boot Settings Configuration          | 46 |

| 3.9.  | S           | ecurity Settings                     | 48 |

| 3.9   | 0.1.        | Change Supervisor Password           | 49 |

| 3.9   | .2.         | Password Check                       | 49 |

| 3.10. | C           | Chipset Settings                     | 50 |

| 3.1   | 0.1.        | North Bridge VIA VX900 Configuration | 51 |

| 3.1   | 0.2.        | South Bridge VIA VX900 Configuration | 60 |

| 3.11. | Е           | xit Options                          | 62 |

| 3.1   | 1.1.        | Save Changes and Exit                | 62 |

| 3.11.2   | 2. Discard Changes and Exit          | 62 |

|----------|--------------------------------------|----|

| 3.11.3   | 3. Discard Changes                   | 62 |

| 3.11.4   | 4. Load Optimal Defaults             | 62 |

| 4. Drive | r Installation                       | 63 |

| 4.1.     | Microsoft Driver Support             | 63 |

| 4.2.     | Linux Driver Support                 | 63 |

| Appendix | A. COMEDB2 Carrier Board Reference   | 65 |

| A.1. Boa | ard Specifications                   | 65 |

| A.2. Ext | ernal I/O Connectors                 | 68 |

| A.2.1.   | . Front I/O                          | 68 |

| A.2.2.   | . Rear I/O                           | 68 |

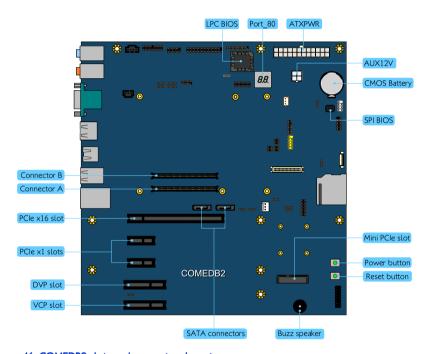

| A.3. CO  | MEDB2 Layout Diagram                 | 69 |

| A.3.1.   | Onboard Slots and Connectors         | 69 |

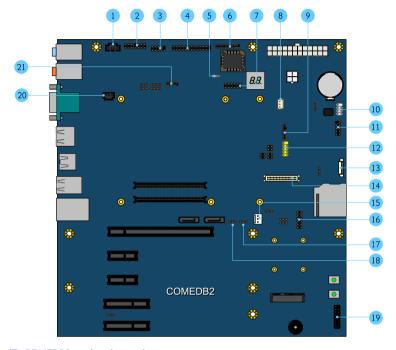

| A.3.2.   | . Onboard Pin headers and Connectors | 70 |

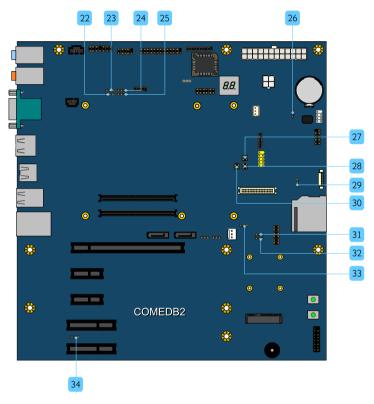

| A.3.3.   | Onboard Jumpers                      | 75 |

# Lists of Figures

| Figure 1: Layout diagram of the COMe-8X90 mainboard (top view)    | 6  |

|-------------------------------------------------------------------|----|

| Figure 2: Layout diagram of the COMe-8X90 mainboard (bottom view) | 6  |

| Figure 3: CPU with heatsink and fan                               | 7  |

| Figure 4: CPU with heatspreader                                   | 7  |

| Figure 5: CPUFAN                                                  | 8  |

| Figure 6: DDR3 SODIMM Sockets                                     | 9  |

| Figure 7: Inserting the memory module                             | 10 |

| Figure 8: Locking the memory module                               | 11 |

| Figure 9: Disengaging the SODIMM locking clips                    | 12 |

| Figure 10: Removing the memory module                             | 12 |

| Figure 11: Heatsink mounting points                               | 13 |

| Figure 12: Heatspreader mounting points                           | 13 |

| Figure 13: Align heatsink on module                               | 14 |

| Figure 14: Align heatspreader on module                           | 14 |

| Figure 15: Carrier board mounting points and connectors           | 15 |

| Figure 16: Installing carrier board hex spacers                   | 16 |

| Figure 17: Aligning COMe-8X90 and carrier board mount points      | 17 |

| Figure 18: Installing heatsink with fan                           | 18 |

| Figure 19: Installing heatspreader                                | 19 |

| Figure 20: Securing COM Express Module (heatsink with fan)        | 20 |

| Figure 21: Securing COM Express Module (heatspreader)             | 21 |

| Figure 22: Illustration of the Main menu screen                   | 24 |

| Figure 23: Illustration of the Advanced Settings screen           | 26 |

| Figure 24: Illustration of the CPU Configuration screen           | 27 |

| Figure 25: Illustration of IDE Configuration screen               | 28 |

| Figure 26: Illustration of Super IO Configuration screen          | 29 |

| Figure 27: Illustration of Hardware Health Configuration screen   | 31 |

| Figure 28: Illustration of ACPI Configuration screen              | 32 |

| Figure 29: Illustration of APM Configuration screen               | 34 |

| Figure 30: Illustration of Spread Spectrum Configuration screen   | 37 |

| Figure 31: Illustration of USB Configuration screen               | 38 |

| Figure 32: Illustration of CRB Configuration screen               | 40        |

|-------------------------------------------------------------------|-----------|

| Figure 33: Illustration of PCI/PnP Settings screen                | 41        |

| Figure 34: Illustration of Boot Settings screen                   | 45        |

| Figure 35: Illustration of Boot Settings Configuration screen     | 46        |

| Figure 36: Illustration of Security Settings screen               | 48        |

| Figure 37: Illustration of Chipset Settings screen                | 50        |

| Figure 38: Illustration of North Bridge VIA VX900 Configuration s | screen51  |

| Figure 39: Illustration of DRAM Frequency/Timing Configuration s  | screen 52 |

| Figure 40: Illustration of OnChip VGA Configuration screen        | 55        |

| Figure 41: Illustration of PCIE-NB Configuration screen           | 58        |

| Figure 42: Illustration of South Bridge VIA VX900 Configuration s | screen 60 |

| Figure 43: Illustration of Exit Options screen                    | 62        |

| Figure 44: Front I/O ports USB2.0 Device Port                     | 68        |

| Figure 45: Rear I/O ports and connectors                          | 68        |

| Figure 46: COMEDB2 slots and connectors layout                    | 69        |

| Figure 47: COMEDB2 pin headers and connectors                     | 70        |

| Figure 48: COMEDB2 jumpers                                        | 75        |

# Lists of Tables

| Table 1: CPU FAN connector pinout                                    | 8  |

|----------------------------------------------------------------------|----|

| Table 2: Serial port addresses and IRQs                              | 29 |

| Table 3: Layout diagram description table of the COMe-8X90 mainboard | 71 |

| Table 4: Layout diagram description table of the COMEDB2 jumpers     | 76 |

# 1. Product Overview

The VIA COMe-8X90 is a compact and highly integrated Type 6 COM Express Module. It comes with an integrated VIA Nano X2 1.2+ GHz NanoBGA2 (or VIA Nano 1.3+ GHz NanoBGA2) processor, boasting of ultra-low power consumption, cool and quiet operation.

The COMe-8X90 is based on the VIA VX900 all-in-one single chipset featuring the Integrated Chrome9™ HD DX9 2D/3D graphics processor and unified video decoding accelerator for rich digital media performance. It provides support for extensive connectivity options, including audio, USB, Ethernet, and graphics, through board-to-board connectors to an I/O carrier board.

# 1.1. Key Components

## 1.1.1. VIA Nano X2 Processor

The VIA Nano™ X2 is a dual-core processor and 64-bit superscalar processor in x86 platform using a 40 nanometer process technology. It delivers an energy-efficient, powerful performance, with cool and quiet operation all within an ultra compact NanoBGA2 package measuring 21mm x 21mm.

VIA Nano X2 processor offers an excellent performance on multitasking application that makes it perfect for embedded system applications such as industrial PCs, test machines, measuring equipment, digital signage, medical PCs, monitoring systems, gaming machines, in-vehicle entertainment, and etc. The VIA Nano X2 processor also boasts of immersive multimedia performance, connectivity and computing applications.

# 1.1.2. VIA VX900 System Chipset

The VIA VX900 Unified Digital Media Chipset is designed to enable high quality digital video streaming and DVD playback in a new generation of fanless, small form factor PCs and IA devices. The VIA VX900 features VIA Chrome9™ HD DX9 2D/3D video processor with MPEG-2, WMV9/VC1, and H.264 video decoding acceleration, DDR3 1066/800 MHz support, motion compensation and dual display support to ensure a rich overall entertainment experience. The VIA VX900 is packed in single chip package measuring 33mm x 33mm.

# 1.2. Product Specifications

## Core Processor

- VIA Nano X2 1.2+GHz NanoBGA2 processor

- VIA Nano 1.3+ GHz NanoBGA2 processor

#### Chipset

VIA VX900 all-in-one system processor

#### System Memory

- o 2 x DDR3 1066 SODIMM socket

- o Supports up to 8GB memory size

#### **On-board BIOS**

- o AMI BIOS,

- o 4/8Mbit SPI flash memory

#### **Operating System**

- o Windows 7

- Windows Embedded System 7

- Windows XP

- Windows XPe

- Windows CE 6.0

- o Linux

#### Hardware Monitoring

- o CPU temperature reading

- o CPU fan speed reading

- System voltage monitoring

#### WatchDog Timer

o Software Programmable

#### **Expansion Bus**

- 1 x PCle Gen2 x4

- o 1 x PCle Gen2 x1

#### Video VGA

Integrated VIA Chrome9™ HD DX9 2D/3D graphics processor and unified video decoding accelerator

#### **CRT Interface**

o 1 x Analog VGA port supports up to 2560x1600 resolution

#### LVDS Interface

1 x LVDS channel supports single-channel 18-bit or 24-bit LVDS panel

#### HDMI® Interface

o 1 x HDMI® port

#### DisplayPort Interface

o 1 x DisplayPort

#### **Expansion Buses**

- 1 x Digital Video Output port for external HDMI<sup>®</sup>/LVDS/DVI transmitter or TV encoder

- 1 x Video Capture port for transport stream input or 8/16-bit CCIR656/601 input

## Ethernet Chipset

o VIA VT6130 Gigabit Ethernet Controller

#### Input/Output Audio

o Support 1 HD audio digital interface

#### LAN

Support 1 LAN port

#### **USB**

- o Support up to 4 USB 3.0 ports (by VLI VL800 controller)

- Support up to 4 USB 2.0 ports

- o Support 1 USB client port (shared with one of USB 2.0 port)

#### **SATA**

Support up to 2 SATA 3.0Gbps ports

#### Serial

Support 2 serial ports with TX and RX signal

### **Expansion Buses**

- o Support 1 SMBus interface

- Support 1 I<sup>2</sup>C bus

- $\circ$  Support 1 GPIO interface with 4 Ins and 4 OUTs (shared with SDIO)

- o Support 1 LPC bus interface

- Support SPI

- Support ExpressCard, speaker out, reset function, thermal protection, suspend/wake signals, power button, power good and fan control signals

Mechanical and Environment

## **COM Express Compliance**

o COM Express™ Type 6, Basic Module

### Dimension

o 95 mm x 125 mm

## **Operating Temperature**

o 0°C up to 60°C

## Storage Temperature

o -40°C to 70°C

## **Operating Humidity**

o 0% to 95°C (relative humidity; non-condensing)

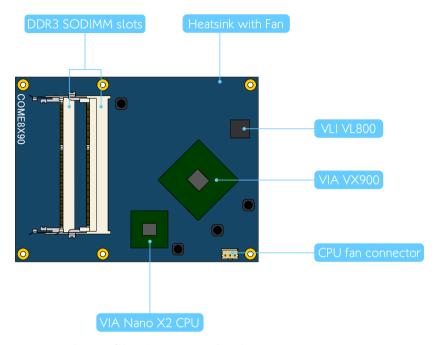

# 1.3. Layout Diagram

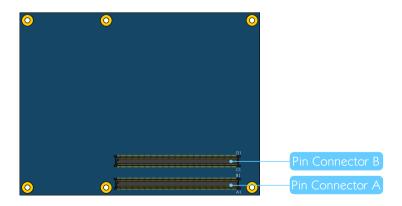

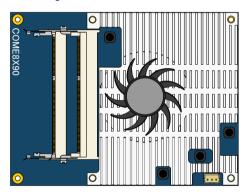

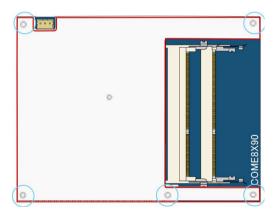

Figure 1: Layout diagram of the COMe-8X90 mainboard (top view)

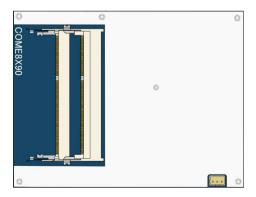

Figure 2: Layout diagram of the COMe-8X90 mainboard (bottom view)

# 2. Hardware Installation

# 2.1. CPU

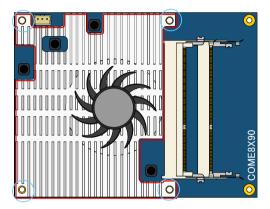

The VIA COMe-8X90 board is designed with the VIA Nano X2 1.2+ GHz processor. Other processor options (e.g., VIA Nano 1.3+ GHz processor) are also available as manufacturing options. The VIA Nano X2 1.2+ GHz processor requires a heatsink with fan/ heatspreader (plus user's own thermal solution) to provide sufficient cooling.

Figure 3: CPU with heatsink and fan

Figure 4: CPU with heatspreader

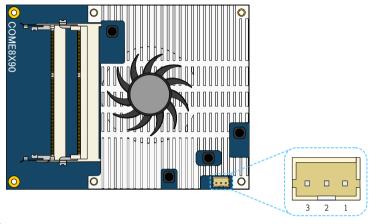

# 2.1.1. CPU Fan Connector: CPUFAN

CPUFAN run on +12V and maintains system cooling.

Figure 5: CPUFAN

| Pin | Signal  |

|-----|---------|

| 1   | FAN_IN  |

| 2   | PWM_OUT |

| 3   | GND     |

Table 1: CPU FAN connector pinout

# 2.2. Memory Module Installation

# 2.2.1. Memory Socket: SODIMM

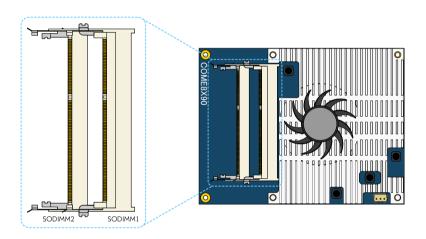

The VIA COMe-8X90 has two DDR3 memory sockets. Each socket can accommodate a maximum of 4 GB memory size. Both slots of COMe-8X90 can therefore support up to 8 GB of 1066 MHz memory. The memory sockets are labeled as "SODIMM1" and "SODIMM2". The location of the DDR3 memory sockets are as shown below.

Figure 6: DDR3 SODIMM Sockets

# 2.2.2. Installing the Memory

## Step 1

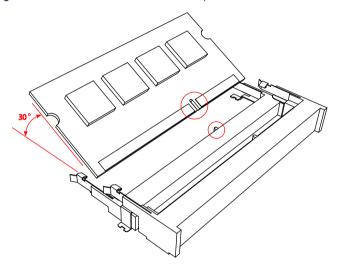

Align the notch on the SODIMM memory module with the protruding wedge on the SODIMM memory socket. Insert the SODIMM memory module at a 30 degree angle relative to the SODIMM memory socket.

Figure 7: Inserting the memory module

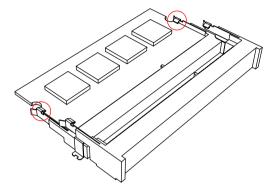

Insert the SODIMM memory module between the two rows of pins. Then push down until the locking clips lock the SODIMM memory module into place. There will be a slight tension as the SODIMM memory module is being locked.

Figure 8: Locking the memory module

# 2.2.3. Removing a Memory Module

## Step 1

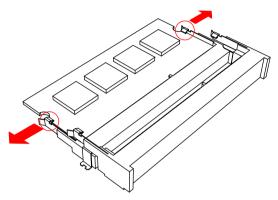

To disengage the locking clips, push the locking clips horizontally outward away from the SODIMM memory module.

Figure 9: Disengaging the SODIMM locking clips

# Step 2

When the locking clips have cleared, the SODIMM memory module will automatically pop up to the 30 degree angle. Remove the memory module.

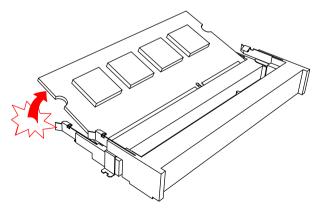

Figure 10: Removing the memory module

# 2.3. Installing Heatsink with fan/Heatspreader on COMe-8X90

## Step 1

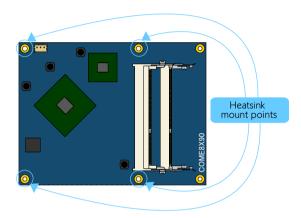

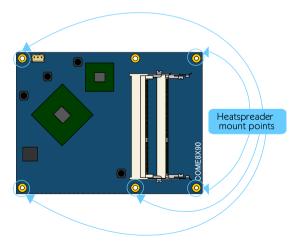

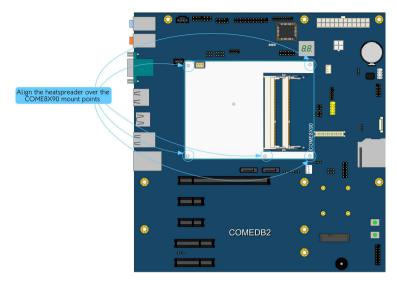

Locate the heatsink/heatspreader mounting holes.

Figure 11: Heatsink mounting points

Figure 12: Heatspreader mounting points

Align the heatsink/heatspreader over the mounting hole on COMe-8X90.

Figure 13: Align heatsink on module

Figure 14: Align heatspreader on module

# 2.4. Mounting COMe-8X90 COM Express to Reference Carrier Board (COMEDB2)

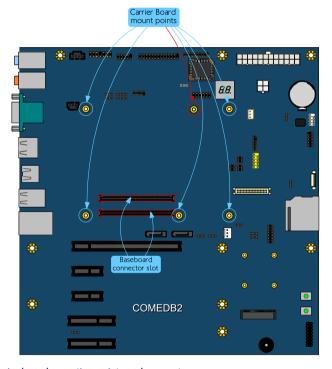

Step 1

First, identify the carrier board mount points (x5) and the connector slots (x2).

Figure 15: Carrier board mounting points and connectors

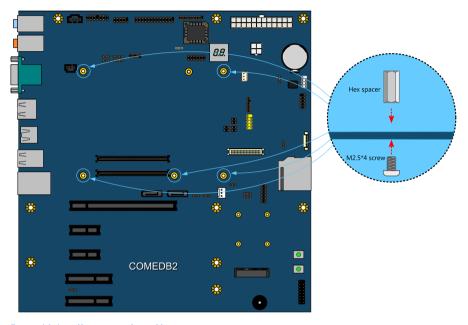

Install the hex spacer onto the carrier board. The hex spacer will be placed on top of the board. From the bottom of the board, tighten the hex spacers by using the  $M2.5 \times 4$ mm screws (x4).

Figure 16: Installing carrier board hex spacers

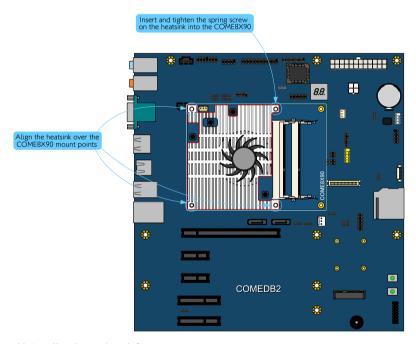

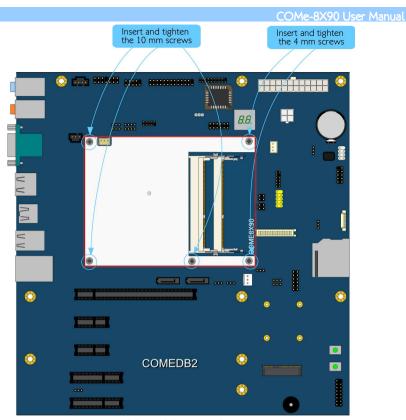

Align the connectors of the COMe-8X90 into the connector slots on the carrier board. Also, align mount points of COMe-8X90 into the hex spacers on the carrier board.

Figure 17: Aligning COMe-8X90 and carrier board mount points

Gently press down the COMe-8X90 board until the pin connectors have been fully inserted into the connector.

## Step 5

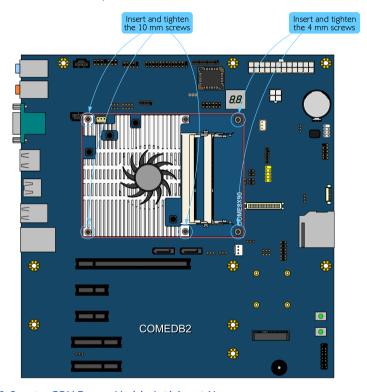

Install the heatsink with fan/heatspreader. Align the heatsink/ heatspreader on the top of COMe-8X90 mount points. Insert the spring screw to secure the heatsink (for heatsink model only).

Figure 18: Installing heatsink with fan

Figure 19: Installing heatspreader

#### Note:

Make sure the thermal pad or thermal paste has been applied on top of the processor and chipset before installing the heatsink/heatspreader.

Securing the COMe-8X90 module by screwing and tightening the screws (10mm and 4mm screws).

Figure 20: Securing COM Express Module (with heatsink)

Figure 21: Securing COM Express Module (with heatspreader)

# 3. BIOS Setup Utility

# 3.1. Entering the BIOS Setup Utility

Power on the computer and press **Delete** during the beginning of the boot sequence to enter the BIOS Setup Utility. If the entry point has passed, restart the system and try again.

# 3.2. Control Keys

**Up** Move up one row

Down Move down one row

**Left** Move to the left in the navigation bar

**Right** Move to the right in the navigation bar

**Enter** Access the highlighted item / Select the item

**Esc** Jumps to the Exit screen or returns to the previous screen

Page up / +1 Increase the numeric value

Page down / - Decrease the numeric value

**F1** General help<sup>2</sup>

**F5** Restore the previous CMOS value

**F9** Load optimized defaults

F10 Save all the changes and exit

#### Note:

1. Must be pressed using the 10-key pad.

2. The General help contents are only for the Status Page and Option Page setup menus

# 3.3. Navigating the BIOS Menus

The main menu displays all the BIOS setup categories. Use the <Left>/<Right> and <Up>/<Down> arrow keys to select any item or sub-menu. Descriptions of the selected/highlighted category are displayed at the bottom of the screen.

The small triangular arrowhead symbol next to a field indicates that a submenu is available (see figure below). Press **<Enter>** to display the sub-menu. To exit the sub-menu, press **<Esc>**.

# 3.4. Getting Help

The BIOS Setup Utility provides a "**General Help**" screen. This screen can be accessed at any time by pressing **F1**. The help screen displays the keys for using and navigating the BIOS Setup Utility. Press **Esc** to exit the help screen.

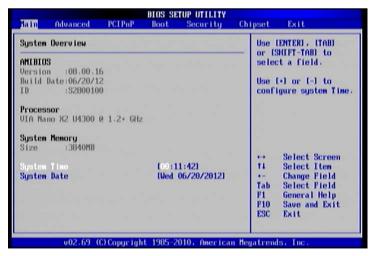

# 3.5. System Overview

The System Overview screen is the default screen that is shown when the BIOS Setup Utility is launched. This screen can be accessed by traversing the navigation bar to the "Main" label.

Figure 22: Illustration of the Main menu screen

## 3.5.1. **AMIBIOS**

The content in this section of the screen shows the current BIOS version, build date, and ID number.

# 3.5.2. Processor

This content in this section shows the CPU information that has been detected.

# 3.5.3. System Memory

This section shows the amount of available memory that has been detected.

# 3.5.4. System Time

This section shows the current system time. Press **Tab** to traverse right and **Shift+Tab** to traverse left through the hour, minute, and second segments. The **+** and **-** keys on the number pad can be used to change the values. The time format is [Hour: Minute: Second].

# 3.5.5. System Date

This section shows the current system date. Press **Tab** to traverse right and **Shift+Tab** to traverse left through the month, day, and year segments. The **+** and - keys on the number pad can be used to change the values. The weekday name is automatically updated when the date is altered. The date format is [Weekday, Month, Day, Year].

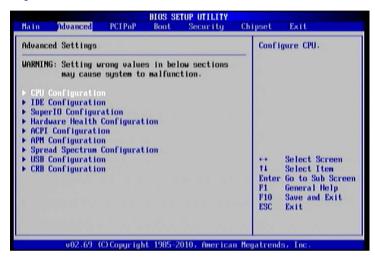

# 3.6. Advanced Settings

The Advanced Settings screen shows a list of categories that can provide access to a sub-screen. Sub-screen links can be identified by the preceding right-facing arrowhead.

Figure 23: Illustration of the Advanced Settings screen

The Advanced Settings screen contains the following links:

- CPU Configuration

- IDE Configuration

- SuperIO Configuration

- Hardware Health Configuration

- ACPI Configuration

- APM Configuration

- Spread Spectrum Configuration

- USB Configuration

- CRB Configuration

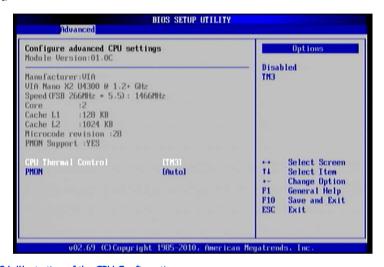

# 3.6.1. CPU Configuration

The CPU Configuration screen shows detailed information about the built-in processor. In addition to the processor information, the thermal controls can be set.

Figure 24: Illustration of the CPU Configuration screen

## 3.6.1.1. CPU Thermal Control

The CPU Thermal Control has two settings: Disabled and TM3. When the setting is changed to "Disabled", the CPU's built-in thermal sensor will not function. When the setting is changed to "TM3", the thermal sensor will automatically adjust the CPU ratio and  $V_{\text{CORE}}$  to prevent the CPU from overheating.

## 3.6.1.2. PMON

The Nano CPU PMON Function has two settings: "Auto" and "Disabled". When set to "Auto", the PMON function will be enabled and controlled the CPU speed to perform automatically at best performance to comply with the given system applications.

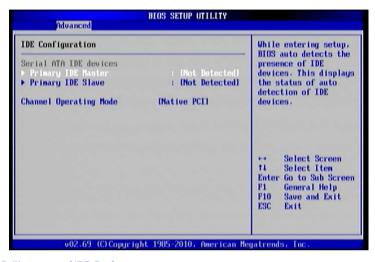

# 3.6.2. IDE Configuration

The IDE Configuration screen shows links to the primary IDE Master and primary IDE Slave hard drive information screens.

Figure 25: Illustration of IDE Configuration screen

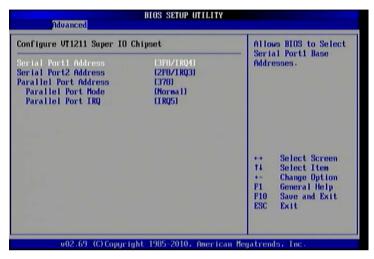

# 3.6.3. Super IO Configuration

The SuperIO Configuration screen shows the specific addresses, IRQs and types of the onboard serial ports.

Figure 26: Illustration of Super IO Configuration screen

### 3.6.3.1. Serial Ports 1 to 2

This option allows the user to select the Serial Port 1 and 2 base I/O address and interrupt request address. The Serial Port 1 to 2 has three selectable options.

| Port | Address and IRQs             |  |  |

|------|------------------------------|--|--|

| 1    | 3F8/IRQ4, 3E8/IRQ4, 2E8/IRQ3 |  |  |

| 2    | 2F8/IRQ3, 3E8/IRQ4, 2E8/IRQ3 |  |  |

Table 2: Serial port addresses and IRQs

## 3.6.3.2. Parallel Port Address

This specifies the I/O port address and IRQ of the parallel port. The parallel port has four options: Disabled, 378, 278 and 3BC

## 3.6.3.3. Parallel Port Mode

This specifies the parallel port mode. The parallel port mode has five options: Normal, Bi-Directional, ECP, EPP, EPP+ECP.

# 3.6.3.4. Parallel Port IRQ

This specifies the parallel port interrupt request address. The parallel port IRQ has 2 options: IRQ5 and IRQ7.

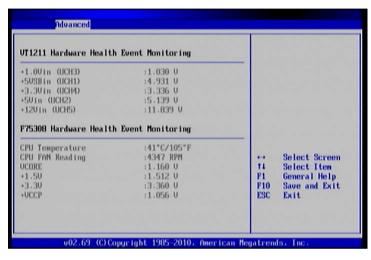

# 3.6.4. Hardware Health Configuration

The Hardware Health Configuration screen displays the monitored aspects of the mainboard such as CPU temperature, system temperature, fan speeds, and voltages of the power planes.

Figure 27: Illustration of Hardware Health Configuration screen

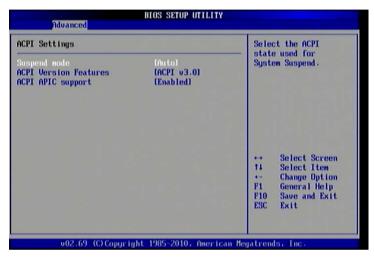

# 3.6.5. ACPI Configuration

ACPI grants the operating system direct control over system power management. The ACPI Configuration screen can be used to set a number of power management related functions.

Figure 28: Illustration of ACPI Configuration screen

## 3.6.5.1. Suspend Mode

The Suspend Mode field has three selectable options.

## S1(POS)

S1/Power On Suspend (POS) is a low power state. In this state, no system context (CPU or chipset) is lost and hardware maintains all system contexts.

## S3(STR)

S3/Suspend To RAM (STR) is a power-down state. In this state, power is supplied only to essential components such as main memory and wakeup-capable devices. The system context is saved to main memory, and context is restored from the memory when a "wakeup" event occurs.

#### Auto

When the Suspend Mode is set to Auto, the operating system will control the power state.

### 3.6.5.2. ACPI Version Features

The ACPI Version Features enables the BIOS to support the designated ACPI specification. There are three versions to choose from: ACPI v1.0, ACPI v2.0, and ACPI v3.0.

## 3.6.5.3. ACPI APIC Support

The ACPI APIC Supports enables the ACPI support in APIC. The ACPI APIC Supports has two options: Enabled and Disabled. When select "Enabled", the ACPI APIC table pointer includes in the Root System Description Table (RSDT) pointer lists. When select "Disabled", support for this feature will be unavailable.

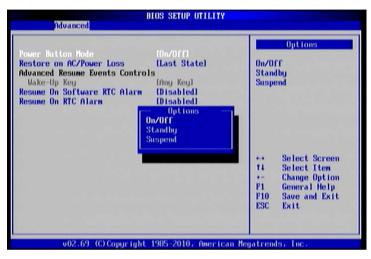

# 3.6.6. APM Configuration

APM enables the operating system to co-work with the BIOS to control the system power management. The APM Configuration screen can be used to set a number of power management functions.

Figure 29: Illustration of APM Configuration screen

#### 3.6.6.1. Power Button Mode

The Power Button Mode has three options.

#### On/Off

When On/Off is selected, pressing the power button will instantly cause the system to power on or off.

## Standby

When Standby is selected, the power button must be pressed and held down for 4 seconds before the system will power off.

## Suspend

When Suspend is selected, pressing the power button will instantly cause the system to enter suspend mode.

### 3.6.6.2. Restore on AC/Power Loss

Restore on AC/Power Loss defines how the system will respond after AC power has been interrupted while the system is on. There are three options.

#### Power Off

The Power Off option keeps the system in an off state until the power button is pressed again.

#### Power On

The Power On option restarts the system when the power has returned.

#### Last State

The Last State option restores the system to its previous state when the power was interrupted.

## 3.6.6.3. Wake-Up Key

The Wake-Up Key feature can only be set when **Resume on PS/2 KBC** is set to "S3" or "S3/S4/S5". Otherwise, this feature will be not selectable. This feature has two options.

## Any Key

The Any Key option enables any key on the keyboard to trigger the Wake-Up event

## Specific Key

The Specific Key option unlocks the Wake-Up Password feature.

# 3.6.6.4. Wake-Up Password

The Wake-Up Password feature can only be set when the **Wake-Up Key** feature is set to "Specific Key". This feature enables the user to specify a key sequence that must be entered in order to wake up the system.

The key sequence can consist of up to 6 alphanumeric characters and some special characters. Function keys and modifier keys (such as Ctrl, Alt, Del, etc.) cannot be used.

## 3.6.6.5. Resume on Software RTC Alarm

Resume on Software RTC Alarm should only be used if the FliteDeck $^{@1}$  S5 resume function will be used on the system. When Resume on Software RTC Alarm is enabled, **Resume on RTC Alarm** will be disabled.

#### 3.6.6.6. Resume on RTC Alarm

Resume on RTC Alarm can only be used if **Resume on Software RTC Alarm** is not enabled. This feature enables the BIOS to automatically power on the system at a scheduled time. When enabled, the **RTC Alarm Date** and **System Time** features will be unlocked.

## 3.6.6.7. RTC Alarm Date (Days)

The RTC Alarm Date feature is visible only when **Resume on RTC Alarm** is enabled. This feature enables the user to specify a specific date each month or daily recurrence. Use the + and - keys on the number pad to change the value of the RTC Alarm Date.

## **Every Day**

The Every Day option triggers the RTC Alarm daily.

#### 1 - 31

When a specific numeric date is selected, the RTC Alarm will be triggered on that day of the month.

## 3.6.6.8. System Time

The System Time option enables the user to specify the time the system should power on for the date that is set in **RTC Alarm Date**.

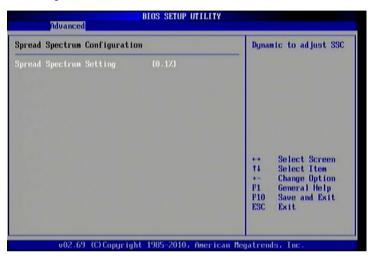

# 3.6.7. Spread Spectrum Configuration

The Spread Spectrum Configuration screen enables access to the CPU Spread Spectrum Setting feature.

Figure 30: Illustration of Spread Spectrum Configuration screen

## 3.6.7.1. Spread Spectrum Setting

The CPU Spread Spectrum Setting feature enables the BIOS to modulate the clock frequencies originating from the mainboard. This feature has two settings: Disabled and 0.1%.

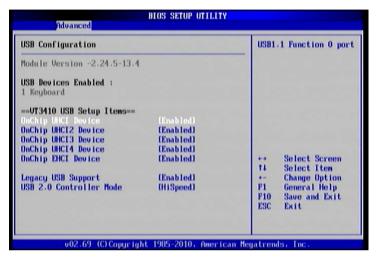

# 3.6.8. USB Configuration

The USB Configuration screen shows the number of connected USB devices. Additionally, support for various USB features can be enabled or disabled.

Figure 31: Illustration of USB Configuration screen

## 3.6.8.1. OnChip UHCI Device

The OnChip UHCI Device feature enables support for USB 1.1 devices. UHCI corresponds with the USB\_1 stack. UCHI2 corresponds with the USB\_2 stack. UCHI3 corresponds with the USB\_3 pin header block. UCHI4 corresponds with the USB\_4 pin header block.

## 3.6.8.2. OnChip EHCl Device

The OnChip EHCI Device feature enables support for USB 2.0 devices on USB 1, USB 2, USB 3, and USB 4.

## 3.6.8.3. Legacy USB Support

The Legacy USB Support feature has two options: "Enabled" and "Auto". When set to "Enabled", the system enables support for legacy USB devices. When set to "Auto", the system automatically disables legacy support if no USB Devices are connected.

## 3.6.8.4. USB 2.0 Controller Mode

Configures the USB 2.0 controller in FullSpeed or HiSpeed. The FullSpeed limit the USB 2.0 controller to transfer data at 12 Mbps. The HiSpeed enables the USB 2.0 controller to transfer data at 480Mbps. The connected USB device must support HiSpeed in order to benefit from this setting.

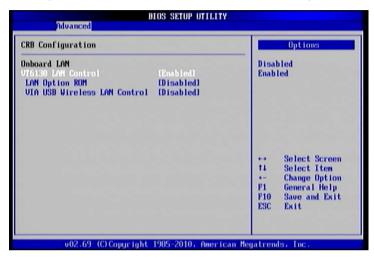

# 3.6.9. CRB Configuration

The CRB Configuration screen includes several chipset settings.

Figure 32: Illustration of CRB Configuration screen

### 3.6.9.1. VT6130 LAN Control

The VT6130 LAN Control feature determines whether the onboard LAN controller will be used or not.

# 3.6.9.2. LAN Option ROM

The LAN Option ROM feature will only be visible if the VT6130 LAN Control feature is enabled. If the LAN Option ROM feature is enabled, then the system will load a separate ROM for the LAN controller in order to boot from Gigabit LAN.

## 3.6.9.3. VIA USB Wireless LAN Control

This feature enables support for USB wireless LAN control: This feature has two options: "Enabled" and "Disabled".

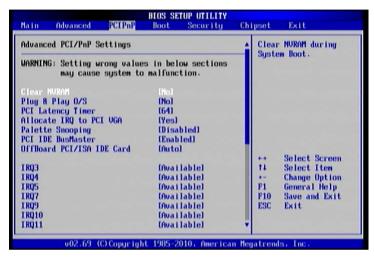

# 3.7. PCI/PnP Settings

The PCI/PnP Settings screen shows the features that relate to PCI bus and Plug and Play devices. Only change these settings if a PCI or Plug and Play device requires it.

Figure 33: Illustration of PCI/PnP Settings screen

## 3.7.1. Clear NVRAM

The Clear NVRAM feature will erase all contents of the non-volatile random access memory when booting up the system. There are two options for this feature: yes and no.

# 3.7.2. Plug & Play O/S

The Plug & Play O/S feature determines whether the operating system or the BIOS controls the configuration of Plug and Play devices. There are two options for this feature.

#### Yes

The Yes option forces the BIOS to ignore any resource conflicts and enables the installed operating system to configure Plug and Play devices.

#### No

The No option gives the BIOS control over handling resource conflicts caused by Plug and Play devices.

# 3.7.3. PCI Latency Timer

The PCI Latency Timer feature enables the user to specify the number of PCI bus cycles a connected PCI device can control before handing control of the PCI bus to the next PCI device waiting to use it. Generally, longer cycles increase PCI performance. The available cycles range from 32 to 248 in increments of 32.

# 3.7.4. Allocate IRQ to PCI VGA

The Allocate IRQ to PCI VGA feature determines whether graphics cards on the PCI bus can access IRQs. This feature has two options.

#### Yes

The Yes option enables the BIOS to respond to a request for an IRQ by a connected PCI VGA card.

#### No

The No option forces the BIOS to ignore all requests for IRQ by a connected PCI VGA card.

# 3.7.5. Palette Snooping

The Palette Snooping feature should be enabled if video decoder cards are being used in the system. When enabled, video decoder cards can retrieve information about the color palette being used by the system's graphics controller. This feature has two options: "Enabled" and "Disabled".

## 3.7.6. PCI IDE BusMaster

The PCI IDE BusMaster feature enables IDE controllers on the PCI bus to directly communicate with IDE hard disks connected to PCI IDE cards. This feature has two options: "Enabled" and "Disabled".

## 3.7.7. OffBoard PCI/ISA IDE Card

Some PCI IDE cards may require this to be set to the PCI slot number (PCI Slot  $1\sim6$ ) that is holding the card.

Auto: Works for most PCI IDE cards.

# 3.7.8. IRQ3~15

The available IRQs range from 3 to 15. However, not all IRQs in the range are available. IRQs 3, 4, 5, 7, 9, 10, 11, 14, and 15 can be set as either "Available" or "Reserved". When set to "Available", any connected PCI or Plug and Play device can use the IRO.

# 3.7.9. DMA Channel 0~7

The available DMA Channels range from 0 to 7. However, not all DMA Channels in the range are available. DMA Channels 0, 1, 3, 5, 6, and 7 can be set as either "Available" or "Reserved". When set to "Available", any connected PCI or Plug and Play device can use the DMA Channel.

# 3.7.10. Reserved Memory Size

The Reserved Memory Size feature enables the user to reserve a portion of the Upper Memory Area for use by legacy devices. The available sizes are 16k, 32k, and 64k. This feature can also be disabled.

# 3.7.11. HotPlug Reserve I/O Port Size

The HotPlug Reserve I/P Port Size feature enables the user to set aside a specified portion of the I/O port block for hot-swappable or CardBus devices. The available options range from 4k to 28k in increments of 4k. There is also an "Auto" option for enabling the BIOS to dynamically choose the size to reserve.

# 3.7.12. HotPlug Reserve Memory Size

The HotPlug Reserve Memory Size feature enables the user to set aside a specified portion of the memory block for hot-swappable or CardBus devices. The available options range from 8MB to 512MB. There is also an "Auto" option for enabling the BIOS to dynamically choose the size to reserve.

# 3.7.13. HotPlug Reserve PFMemory Size

The HotPlug Reserve PFMemory Size feature enables the user to set aside a specified portion of the pre-fetch memory block for hot-swappable or CardBus devices. The available options range from 32MB to 2048MB. There is also an "Auto" option for enabling the BIOS to dynamically choose the size to reserve.

# 3.8. Boot Settings

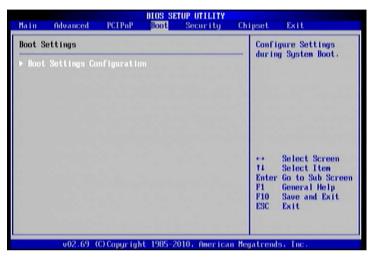

The Boot Settings screen has one link that goes to the **Boot Settings Configuration** screen.

Figure 34: Illustration of Boot Settings screen

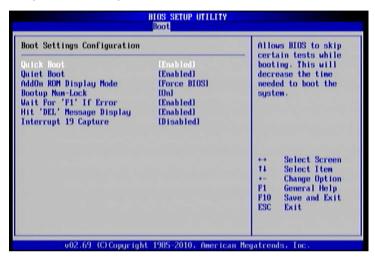

# 3.8.1. Boot Settings Configuration

The Boot Settings Configuration screen has several features that can be run during the system boot sequence.

Figure 35: Illustration of Boot Settings Configuration screen

## 3.8.1.1. Quick Boot

The Quick Boot feature enables the BIOS to skip certain tests in order to speed up the boot sequence. This feature has two options: "Enabled" and "Disabled"

## 3.8.1.2. Quiet Boot

The Quiet Boot feature hides all of the Power-on Self Test (POST) messages during the boot sequence. Instead of the POST messages, the user will see an OEM logo. This feature has two options: enabled and disabled.

## 3.8.1.3. AddOn ROM Display Mode

The AddOn ROM Display Mode feature determines whether or not information from option ROMs is displayed during the boot sequence. There are two options for this feature: "Force BIOS" and "Keep Current". The "Force BIOS" option ensures that all information from option ROMs is displayed.

## 3.8.1.4. Bootup Num-Lock

The Bootup Num-Lock feature determines how the 10-key pad will behave. When the feature is enabled, the 10-key pad will behave as a number pad. When the feature is disabled, the 10-key pad will behave as cursor navigation keys.

#### 3.8.1.5. Wait for 'F1' if Error

This feature determines how the system will respond if an error is detected during the boot sequence. If this feature is enabled, the BIOS will pause booting and wait for the user to press F1 to enter the BIOS setup menu. This feature has two options: enabled and disabled.

## 3.8.1.6. Hit 'DEL' Message Display

This feature determines if the BIOS will display a POST message that informs the user how to access the BIOS Setup Utility. This feature has two options: enabled and disabled.

## 3.8.1.7. Interrupt 19 Capture

The Interrupt 19 Capture feature enables hard drives attached to add-on host adaptors (e.g., SCSI cards, eSATA cards, etc) to function as bootable hard drives. Enabling this feature will also grant access to any existing ROM BIOS utilities on the host adapter. This feature has two options: "Enabled" and "Disabled".

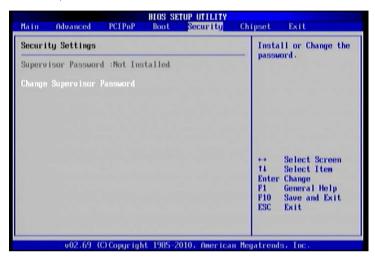

# 3.9. Security Settings

The Security Settings screen provides a way to restrict access to the BIOS or even the entire system.

Figure 36: Illustration of Security Settings screen

# 3.9.1. Change Supervisor Password

This option is for setting a password for accessing the BIOS setup utility. When a password has been set, a password prompt will be displayed whenever the BIOS setup utility is launched. This prevents an unauthorized person from changing any part of the system configuration.

When a supervisor password is set, the **Password Check** option will be unlocked.

## 3.9.2. Password Check

This feature is compulsory when the **Change Supervisor Password** option is set. The user will have up to three chances to enter the correct password before the BIOS forces the system to stop booting. If the user does not enter the correct password, the keyboard will also lock up. The only way to get past this is to do a hard reboot (i.e., use the system reset button or cut off the power to the system). A soft reboot (i.e., Ctrl+Alt+Del) will not work because the keyboard will be locked. This feature has two options.

### Setup

The Setup option forces users to enter a password in order to access the BIOS Setup Utility.

# Always

The Always option forces users to enter a password in order to boot up the system.

# 3.10. Chipset Settings

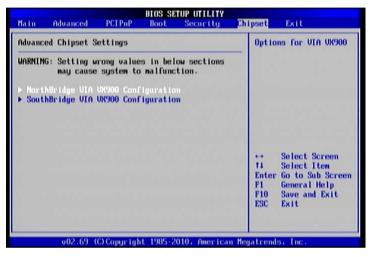

The Chipset Settings screen has two links for accessing North and South bridge functions. Though the VX900 is a single chip solution, the North and South bridge categories are still for grouping features.

Figure 37: Illustration of Chipset Settings screen

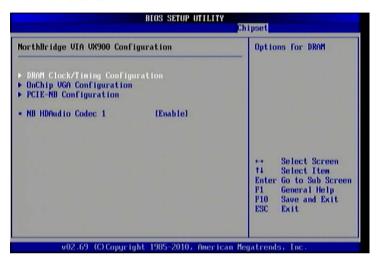

# 3.10.1. North Bridge VIA VX900 Configuration

The North Bridge VIA VX900 Configuration screen contains four links to subscreens and two features.

Figure 38: Illustration of North Bridge VIA VX900 Configuration screen

#### 3.10.1.1. NB HDAudio Codec 1

The NB HDAudio Codec 1 feature enables the BIOS to control the high definition audio codec in the chipset. This feature has two options: "Enable" and "Disable".

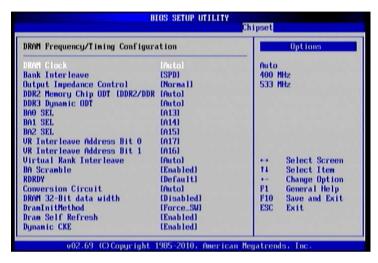

## 3.10.1.2. DRAM Clock/Timing Configuration

The DRAM Clock/Timing Configuration screen has one feature for controlling the system DRAM. All other DRAM features are automated and cannot be accessed.

Figure 39: Illustration of DRAM Frequency/Timing Configuration screen

#### 3.10.1.2.1. DRAM Clock

The DRAM Clock option enables the user to determine how the BIOS handles the memory clock frequency. The memory clock can either be dynamic or static. This feature has three options.

#### Auto

The Auto option enables the BIOS to select a compatible clock frequency for the installed memory.

#### 400 MHz

The 400 MHz option forces the BIOS to be fixed at 800 MHz for DDR3 memory modules.

#### 533 MHz

The 533 MHz option forces the BIOS to be fixed at 1066 MHz for DDR3 memory modules.

#### 3.10.1.2.2. Bank Interleave

This item is for setting the interleave mode of the SDRAM interface. Interleaving allows banks of SDRAM to alternate their refresh and access cycles. One bank will undergo its refresh cycle while another is being accessed. This improves performance of the SDRAM by masking the refresh time of each bank

This feature has 5 options: "SPD", "Non-Page", "2-Way", "4-Way" and "8-Way".

#### 3.10.1.2.3. Output Impedance Control

This feature has 2 options: "Normal" and "Weak".

## 3.10.1.2.4. DDR2 Memory Chip ODT [DDR2/DDR

This feature has 7 options: "Auto", "Disabled", "75 ohm/60 ohm", "150 ohm/120 ohm", "50 ohm/40 ohm", "NA/20 ohm" and "NA/30 ohm".

#### 3.10.1.2.5. DDR3 Dynamic ODT

This feature has 4 options: "Auto", "Disabled", "R2Q/4" and "R2Q/2".

#### 3.10.1.2.6. BA0 SEL

This feature has 5 options: "A11", "A13", "A15", "A17" and "A19".

#### 3.10.1.2.7. BA1 SEL

This feature has 5 options: "A12", "A14", "A16", "A18" and "A20".

#### 3.10.1.2.8. BA2 SEL

This feature has 4 options: "A14", "A15", "A18" and "A19".

#### 3.10.1.2.9. VR Interleave Address Bit 0

This feature has 4 options: "A15", "A17", "A19" and "A21".

#### 3.10.1.2.10. VR Interleave Address Bit 1

This feature has 4 options: "A14", "A16", "A18" and "A20".

#### 3.10.1.2.11. Virtual Rank Interleave

This feature has 2 options: "Auto" and "Disabled".

#### 3.10.1.2.12. BA Scramble

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.2.13. RDRDY

This feature has 2 options: "Slowest" and "Default".

#### 3.10.1.2.14. Conversion Circuit

This feature has 2 options: "Auto" and "Async".

#### 3.10.1.2.15. DRAM 32-Bit data width

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.2.16. DramInitMethod

This feature has 2 options: "Auto" and "Force\_SW".

#### 3.10.1.2.17. Dram Self Refresh

This feature has 2 options: "Disabled" and "Enabled".

#### 3.10.1.2.18. Dynamic CKE

This feature has 2 options: "Disabled" and "Enabled".

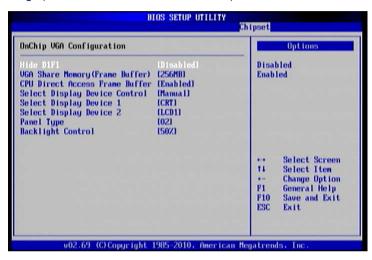

## 3.10.1.3. OnChip VGA Configuration

The OnChip VGA Configuration screen has features for controlling the integrated graphics controller in the VX900 chipset.

Figure 40: Illustration of OnChip VGA Configuration screen

#### 3.10.1.3.1. Hide D1F1

This feature has 2 options: "Disabled" and "Enabled".

#### 3.10.1.3.2. VGA Share Memory (Frame Buffer)

The VGA Share Memory feature enables the user to choose the amount of the system memory to reserve for use by the integrated graphics controller. The amount of memory that can be reserved ranges from 64 - 512 MB.

#### 3.10.1.3.3. CPU Direct Access Frame Buffer

The CPU Direct Access Frame Buffer feature enables the CPU to write to the portion of memory reserved for the integrated graphics controller. This feature has two options: "Disabled" and "Enabled".

## 3.10.1.3.4. Select Display Device Control

This feature has 2 options: "Auto" and "Manual".

### 3.10.1.3.5. Select Display Device 1 and 2

The Select Display Device feature enables the user to choose a specific display interface. This feature has four options: CRT, LCD, HDMI and DP. If both Select Display Device 1 and Select Display Device 2 are set to the same interface, then any display device connected to the other interface will not function. For example, if both Select Display 1 and 2 are set to CRT, then no data will be sent to the HDMI, LCD and DP port.

### 3.10.1.3.6. Panel Type

The Panel Type feature enables the user to specify the resolution of the display being used with the system. The panel types are predefined in the VGA VBIOS.

| Panel Type | Resolution  | Panel Type | Resolution  |

|------------|-------------|------------|-------------|

| 00         | 640 × 480   | 08         | 800 × 480   |

| 01         | 800 × 600   | 09         | 1024 × 600  |

| 02         | 1024 × 768  | 10         | 1366 x 768  |

| 03         | 1280 × 768  | 11         | 1600 x 1200 |

| 04         | 1280 × 1024 | 12         | 1680 × 1050 |

| 05         | 1400 × 1050 | 13         | 1920 × 1200 |

| 06         | 1440 × 900  | 14         | 1920 × 1080 |

| 07         | 1280 × 800  | 15         | 1024 × 576  |

## 3.10.1.3.7. Backlight Control

The Backlight Control feature control enables the user to control the brightness of the LCD backlight. This feature has five options.

Level 1 0% PW Duty

Level 1 25% PW Duty

Level 2 50% PW Duty

Level 3 75% PW Duty

Level 4 100% PW Duty

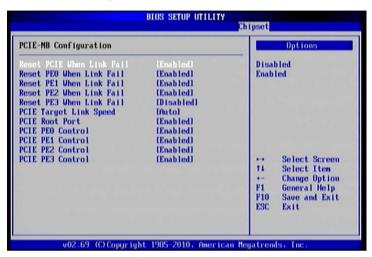

# 3.10.1.4. PCIE-NB Configuration

The PCIE-NB Configuration screen has features for controlling the PCIE Express interface in the VX900 chipset.

Figure 41: Illustration of PCIE-NB Configuration screen

### 3.10.1.4.1. Reset PCIE When Link Fail

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.4.2. Reset PE0 When Link Fail.

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.4.3. Reset PE1 When Link Fail

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.4.4. Reset PE2 When Link Fail

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.4.5. Reset PE3 When Link Fail

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.4.6. PCIE Target Link Speed

This feature has 2 options: "Auto" and "Force Gen1".

#### 3.10.1.4.7. PCIE Root Port

This feature has 2 options: "Enabled" and "Disabled".

### 3.10.1.4.8. PCIE PE0 Control

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.4.9. PCIE PE1 Control

This feature has 2 options: "Enabled" and "Disabled".

#### 3.10.1.4.10. PCIE PE2 Control

This feature has 2 options: "Enabled" and "Disabled".

### 3.10.1.4.11. PCIE PE3 Control

This feature has 2 options: "Enabled" and "Disabled".

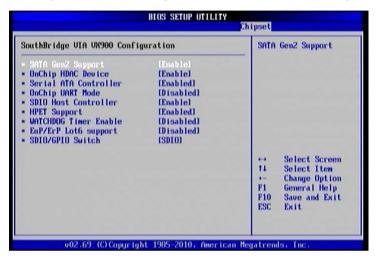

# 3.10.2. South Bridge VIA VX900 Configuration

The South Bridge VIA VX900 Configuration screen has the following features.

Figure 42: Illustration of South Bridge VIA VX900 Configuration screen

# 3.10.2.1. SATA Gen2 Support

The SATA Gen2 Support feature enables to BIOS to determine whether SATA 3Gb/s or 1.5Gb/s specifications are followed. This feature has two options: "Enabled" or "Disabled".

## 3.10.2.2. On Chip HDAC Device

The OnChip HDAC Device feature enables the BIOS to control the high definition audio codec in the chipset. This feature has two options: "Enable" or "Disable".

## 3.10.2.3. Serial ATA Controller

The Serial ATA Controller feature enables the BIOS to turn the SATA controller in the chipset ON or OFF. This feature has two options: "Enabled" or "Disabled".

# 3.10.2.4. OnChip UART Mode

This feature has two options: "Enabled" or "Disabled".

#### 3.10.2.5. SDIO Host Controller

This feature has two options: "Enable" or "Disable".

## 3.10.2.6. HPET Support

The HPET Support feature enables the BIOS to determine if the high precision event timer in the chipset is ON or OFF. This feature has two options: "Enabled" or "Disabled".

#### 3.10.2.7. WATCHDOG Timer Enable

The WATCHDOG Timer Enable feature unlocks three other features that enable the BIOS to monitor the state of the system. This feature has two options: "Enabled" or "Disabled".

## 3.10.2.8. EuP/ErP Lot6 support

The EuP/ErP Lot6 Support feature enables the BIOS to reduce the power draw to less than 1W when the system is in standby mode. This feature has two options: enabled and disabled.

## 3.10.2.9. SDIO/GPIO Switch

Switch between SDIO and GPIO.

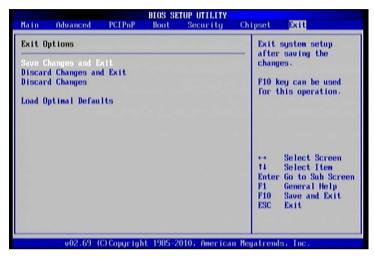

# 3.11. Exit Options

Figure 43: Illustration of Exit Options screen

# 3.11.1. Save Changes and Exit

Save all changes to the BIOS and exit the BIOS Setup Utility. The "F10" hotkey can also be used to trigger this command.

# 3.11.2. Discard Changes and Exit

Exit the BIOS Setup Utility without saving any changes. The "Esc" hotkey can also be used to trigger this command.

# 3.11.3. Discard Changes

Undo the previous changes.

# 3.11.4. Load Optimal Defaults

Load optimal default values for all the setup items. The default optimized values are defined by the mainboard manufacturer to provide optimized environment for a basic system. The "F9" hotkey can also be used to trigger this command.

# 4. Driver Installation

## 4.1. Microsoft Driver Support

The VIA COMe-8X90 mainboard is compatible with Microsoft operating systems. The latest Windows drivers can be downloaded from the VEPD website at www.viaembedded.com.

For embedded operating systems, the related drivers can be found in the VIA Embedded website at www.viaembedded.com.

## 4.2. Linux Driver Support

The VIA COMe-8X90 mainboard is highly compatible with many Linux distributions.

Support and drivers are provided through various methods including:

- Drivers provided by VIA

- Using a driver built into a distribution package

- Visiting www.viaembedded.com for the latest updated drivers

- Installing a third party driver (such as the ALSA driver from the Advanced Linux Sound Architecture project for integrated audio)

For OEM clients and system integrators developing a product for long term production, other code and resources may also be made available. Contact VEPD to submit a request.

# Appendix A. COMEDB2 Carrier Board Reference

## A.1. Board Specifications

- COM Express Module Type

- o Support Type 6

- Audio

- VIA VT1828S High Definition Audio Codec

- Super I/O

- VIA VT1211 LPC Super I/O

- BIOS

- AMI BIOS

- o 4/8Mbit LPC Flash BIOS, PLCC 32 pin or SPI BIOS

- Front I/O Connector

- o 1 x SD card connector (SDIO), shared with DIO1 pin header

- o 1 x USB client type A connector, share with USB2.0 port3.

#### Rear I/O Connector

- 1 x VGA connector

- 1 x COM connector

- 1 x DisplayPort (DP2)

- o 1 x HDMI® port

- o 4 x USB 3.0 connector

- o 1 x RJ-45 GigaLAN port (Gigabit Ethernet)

- o 6 x Audio jacks (support multi-channel audio outputs)

#### Onboard Pin Header

- o 1 x COM2 pin header, add +5V/+12V power select option on RI pin

- o 1 x LPT pin header

- o 1 x SPI pin header

- o 1 x LPC pin header

- o 1 x DIO1 pin header, shared with SDIO port

- o 1 x DIO2 pin header (from VIA VT1211)

- o 1 x SMBus pin header

- o 1 x I<sup>2</sup>C pin header

- o 2 x USB 2.0 pin headers for USB 2.0 port 0~3

- o 1 x Front LAN LED pin header

- o 1 x Front Audio pin header

- o 1 x Front Panel pin header (for HDD LED, Power LED, Switch and Speaker)

#### Onboard Jumper

- 1 x Clear CMOS jumper

- o 1 x Inverter Voltage Select jumper

- o 1 x Panel Power Select jumper

- o 2 x BIOS Type Select jumpers (for selecting LPC/SPI BIOS)

- o 2 x BIOS Select jumper (for selecting Module/Carrier board BIOS)

- o 2 x COM power select jumper

- 1 x TV/DVP jumper select

- o 2 x USB 2.0 port select jumper

- o 1 x USB 2.0 to Mini PCIe slot select jumper

- o 1 x USB 2.0 Device Port select jumper

#### Switch

- o 1 x Power button switch

- 1 x Reset switch

#### Form Factor and Dimension

- Micro-ATX

- o 6 Layers

- o 10 inch x 9 6 inch

#### Operating Temperature

o 0°C up to 60°C

#### • Storage Temperature

-40°C up to 70°C

#### • Operating and Storage Humidity

o -95% relative humidity

#### Operating System

- Microsoft Windows 7

- Microsoft Windows XP

- o Microsoft Windows XPe

- Microsoft Windows CE 6.0

- o Microsoft Windows Embedded Standard 7

- o Linux

#### A.2. External I/O Connectors

The COMEDB2 has a wide selection of interfaces. It includes a selection of frequently used ports as part of the external I/O coastline.

#### A.2.1. Front I/O

Figure 44: Front I/O ports USB2.0 Device Port

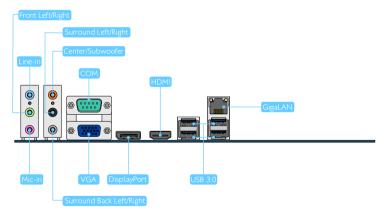

#### A.2.2 Rear I/O

Figure 45: Rear I/O ports and connectors

# A.3. COMEDB2 Layout Diagram

#### A.3.1. Onboard Slots and Connectors

Figure 46: COMEDB2 slots and connectors layout

#### A.3.2. Onboard Pin headers and Connectors

Figure 47: COMEDB2 pin headers and connectors

| Item | Description                                   |

|------|-----------------------------------------------|

| 1    | CD_IN: Audio cable connector from CD drive    |

| 2    | F_AUDIO: Front audio pin header               |

| 3    | COM2: COM2 pin header                         |

| 4    | LPT: LPT pin header                           |

| 5    | SYS_SEN: System Sensor pin header             |

| 6    | LPC: LPC pin header                           |

| 7    | DIO2: DIO2 pin header                         |

| 8    | CPUFAN: CPU fan                               |

| 9    | USB2_0/1: USB 2.0 pin header for port 0 and 1 |

| 10   | SPI: SPI pin header                           |

| 11 | SER_PORT: Serial Port pin header             |

|----|----------------------------------------------|

| 12 | USB2_2/3: USB2.0 pin header for port 2 and 3 |

| 13 | INVERTER: Inverter connector                 |

| 14 | LVDS: LVDS connector                         |

| 15 | SYSFAN: System fan connector                 |

| 16 | DIO1: DIO1 connector                         |

| 17 | I2C_BUS: I <sup>2</sup> C pin header         |

| 18 | SMBUS: System Management Bus pin header      |

| 19 | F_PANEL: Front Panel pin header              |

| 20 | SPDIF: SPDIF connector                       |

| 21 | F_PANEL: Front LAN LED pin header            |

Table 3: Layout diagram description table of the COMe-8X90 mainboard

1 CD\_IN\_L

2 CD\_IN\_GND

3 CD\_IN\_GND

4 CD\_IN\_R

#### 3 COM2

| COM_DCD2 | 1 | 2  | COM_RXD2 |

|----------|---|----|----------|

| COM_TXD2 | 3 | 4  | COM_DTR2 |

| GND      | 5 | 6  | COM_DSR2 |

| COM_RTS2 | 7 | 8  | COM_CTS2 |

| COM_RI2  | 9 | 10 | KEY      |

### 2 F\_AUDIO

| MIC2_FR_L    | 1 1 | 8        | 2  | AGND     |

|--------------|-----|----------|----|----------|

| MIC2_FR_R    | 3   |          | 4  | FNT_DET  |

| HP_OUT_R     | 5 ( | <b>ᡂ</b> | 6  | MIC2_JD  |

| FNT_IO_SENSE | 7   |          | 8  | KEY      |

| HP_OUT_L     | 9 1 | <b>ᡂ</b> | 10 | LINE2_JD |

| +12V         | 11  |          | 12 | +12V     |

| AGND         | 13  |          | 14 | AGND     |

|              |     |          |    |          |

#### 4 LPT

| -LP_STB | 1  | 2  | -LP_AFD  |

|---------|----|----|----------|

| LP_D0   | 3  | 4  | -LP_ERR  |

| LP_D1   | 5  | 6  | -LP_INIT |

| LP_D2   | 7  | 8  | -LP_SLIN |

| LP_D3   | 9  | 10 | GND      |

| LP_D4   | 11 | 12 | GND      |

| LP_D5   | 13 | 14 | GND      |

| LP_D6   | 15 | 16 | GND      |

| LP_D7   | 17 | 18 | GND      |

| -LP_ACK | 19 | 20 | GND      |

| LP_BUSY | 21 | 22 | GND      |

| LP_PE   | 23 | 24 | GND      |

| LP_SLCT | 25 | 26 | KEY      |

#### 5 SYS\_SEN

1 DTDP

2 DTDP

3 GND

#### 8 CPUFAN

1 FANIO 2 FANPWM 3 GND

#### 6 LPC

| LPC_AD1    | 1  |              | 2  | LPC_33M_CLK |

|------------|----|--------------|----|-------------|

| -LPC_RESET | 3  | $\mathbf{x}$ | 4  | GND         |

| LPC_AD0    | 5  | <b>3</b>     | 6  | NC          |

| LPC_AD2    | 7  | •            | 8  | -LPC_FRAME  |

| LPC_SERIRQ | 9  |              | 10 | LPC_AD3     |

| -LPC_DRQ1  | 11 | •            | 12 | NC          |

| +5V        | 13 | *            | 14 | +3.3V       |

| +5V        | 15 | ***          | 16 | +3.3V       |

| GND        | 17 | 35           | 18 | GND         |

| GND        | 19 |              | 20 | KEY         |

#### 9 USB2\_0/1

| VUSB     | 1  | 2  | VUSB       |

|----------|----|----|------------|

| USBD_T4- | 3  | 4  | USBD_T5-   |

| USBD_T4+ | 5  | 6  | USBD_T5+   |

| GND      | 7  | 8  | GND        |

| KEY      | 9  | 10 | W_LESS_LED |

| GND      | 11 | 12 | -RF_ON     |

#### 7 DIO2

| 5V_DIO2   | 1  |   | 2  | 12V_DIO2  |

|-----------|----|---|----|-----------|

| SIO_GPO30 | 3  | • | 4  | SIO_GPI34 |

| SIO_GPO31 | 5  | • | 6  | SIO_GPI35 |

| SIO_GPO32 | 7  |   | 8  | SIO_GPI36 |

| SIO_GPO33 | 9  |   | 10 | SIO_GPI37 |

| GND       | 11 |   | 12 | GND       |

#### 10 SPI

| SPI_VCC  | 1 _ 2      | GND     |

|----------|------------|---------|

| -SPI_SS0 | 3 🙃 🕠 4    | SPI_CLK |

| SPI_DI   | 5 \cdots 6 | SPI_DO  |

| KFY      | 7 🕒 8      | RESET   |

#### SER\_PORT

| SER0_TX_CON | 1   | 2  | SER0_RX_CON |

|-------------|-----|----|-------------|

| NC          | 3   | 4  | NC          |

| GND         | 5 🚥 | 6  | NC          |

| SER1_TX_CON | 7 🚟 | 8  | SER1_RX_CON |

| NC          | 9   | 10 | KEY         |

#### 12 USB2\_2/3

| VUSB     | 1   | 2  | VUSB     |

|----------|-----|----|----------|

| USBD_T6- | 3   | 4  | USBD_T7- |

| USBD_T6+ | 5 🙃 | 6  | USBD_T7+ |

| GND      | 7   | 8  | GND      |

| KEY      | 9   | 10 | GND      |

#### 13 Inverter

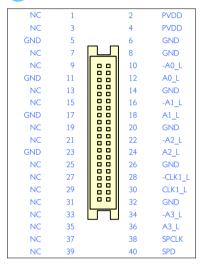

#### 14 LVDS

#### 15 SYSFAN

| - 1 | EANIO  |     |

|-----|--------|-----|

| 1   | FANIO  |     |

| 2   | FANPWM |     |

| 2   | CND    | - L |

| 3   | GND    |     |

#### 16 DIO1

| 5V_DIO1  | 1    | 2  | 12V_DIO1 |

|----------|------|----|----------|

| COM_GPO0 | 3 💶  | 4  | COM_GPI0 |

| COM_GPO1 | 5    | 6  | COM_GPI1 |

| COM_GPO2 | 7 🚟  | 8  | COM_GPI2 |

| COM_GPO3 | 9    | 10 | COM_GPI3 |

| GND      | 11 💶 | 12 | GND      |

#### **I2C BUS**

I2C\_CLK

3

2 I2C\_DATA GND

000

## 21 FLAN\_LED

3VSUS -LAN\_ACT 3VSUS NC W\_LAN\_LED GND 3VSUS GND KEY GND

#### 18 SMBUS

SMB\_CLK 2 SMB\_DATA

GND

000

#### 19 F\_PANEL

| FP_5V | 1  |           | 2  | FP_3V     |

|-------|----|-----------|----|-----------|

| FP_5V | 3  | 32        | 4  | -SATA_LED |

| -PLED | 5  | **        | 6  | -PW_BTN   |

| FP_5V | 7  | <b></b>   | 8  | GND       |

| NC    | 9  | œ         | 10 | RST_SW    |

| NC    | 11 | <b>92</b> | 12 | GND       |

| SPEAK | 13 | <b>33</b> | 14 | FP_5V     |

| KEY   | 15 |           | 16 | NC        |

#### 20 SPDIF

+5V

2 **SPDIFO** GND

## A.3.3. Onboard Jumpers

Figure 48: COMEDB2 jumpers

| Item | Description                                                  |

|------|--------------------------------------------------------------|

| 22   | BIOS_SEL0: Module and carrier board BIOS select jumper       |

| 23   | BIOS_SEL1: Module and carrier board BIOS select jumper       |

| 24   | JP_COM2_VSEL: COM2 voltage select jumper                     |

| 25   | JP_COM1_VSEL: COM1 voltage select jumper                     |

| 26   | CLEAR_CMOS: Clear CMOS jumper                                |

| 27   | JP_USB3_SEL: USB 2_3 enabled select jumper                   |

| 28   | JP_USB2_SEL: USB 2_2 enabled select jumper                   |

| 29   | IVDD: Inverter power select jumper                           |

| 30   | JP_USBME_SEL: USB port 2 and PCIE slot enabled select jumper |

| 31   | BIOS_DIS1: Module and carrier board BIOS select jumper       |

| 32   | BIOS_DIS0: Module and carrier board BIOS select jumper       |

| 33   | PVDD: LCD panel power select jumper                          |

| 34   | TV_DVP_SEL: TV and DVP select jumper                         |

Table 4: Layout diagram description table of the COMEDB2 jumpers

22 BIOS\_SEL0

23 BIOS\_SEL1

| BIOS_SEL0 | BIOS_SEL1 |                                  |

|-----------|-----------|----------------------------------|

| Pi        | ns        | Description                      |

| 1-2       | 2-3       | Select module SPI BIOS (default) |

| 2-3       | 1-2       | Select carrier LPC BIOS          |

| 1-2       | 2-3       | Select carrier SPI BIOS          |

# 24 JP\_COM2\_VSEL

| Pins | Description                             |

|------|-----------------------------------------|

| 1-2  | Enabled COM2 pin header to support +5V  |

| 2-3  | Normal (default)                        |

| 3-4  | Enabled COM2 pin header to support +12V |

## 25 JP\_COM1\_VSEL

| Pins | Description                             |

|------|-----------------------------------------|

| 1-2  | Enabled COM1 pin header to support +5V  |

| 2-3  | Normal (default)                        |

| 3-4  | Enabled COM1 pin header to support +12V |

### 26 CLEAR\_CMOS

| Pins | Description                 |

|------|-----------------------------|

| 1-2  | Keep CMOS setting (default) |

| 2-3  | Clear CMOS setting          |

## 27 JP\_USB3\_SEL

| Pins | Description                               |

|------|-------------------------------------------|

| 1-2  | Enabled USB 2.0 Port 3 (USB2_3) (default) |

| 3-4  | Enabled USB 2.0 Port 3 (USB2_3) (default) |

## 28 JP\_USB2\_SEL

| Pins | Description                               |

|------|-------------------------------------------|

| 1-2  | Enabled USB 2.0 Port 2 (USB2_2) (default) |

| 3-4  | Enabled USB 2.0 Port 2 (USB2_2) (default) |

Note: For 29 IP USB2 SFI to be activated 31 IP USBMF SFI has to be disabled

#### 29 IVDD

| Pins | Description                               |

|------|-------------------------------------------|

| 1-2  | Use +5V for the Inverter power.           |

| 2-3  | Use +12V for the Inverter power (default) |

#### 30 JP\_USBME\_SEL

| Pins | Description                              |

|------|------------------------------------------|

| 1-2  | Enabled USB 2.0 port 2 to Mini PCIE slot |

| 3-4  | Enabled USB 2.0 port 2 to Mini PCIE slot |

Note: For 31 IP USB2 SEL to be activated. 29 IP USBME SEL has to be disabled.

#### 31 BIOS\_DIS1

# 32 BIOS\_DIS0

| BIOS_DIS1 | BIOS_DIS01 |                                  |

|-----------|------------|----------------------------------|

| Pins      |            | Description                      |

| 1-2       | 2-3        | Select module SPI BIOS (default) |

| 2-3       | 1-2        | Select carrier LPC BIOS          |

| 1-2       | 2-3        | Select carrier SPI BIOS          |

# 33 PVDD

| Pins | Description                                 |

|------|---------------------------------------------|

| 1-2  | Use +5V for the LCD panel power.            |

| 2-3  | Use +3.3V for the LCD panel power (default) |

## 34 TV\_DVP\_SEL

| Pins | Description                          |

|------|--------------------------------------|

| 1-2  | Enabled TTL/TV support from DVP slot |

| 2-3  | Plug detect from DVP slot (default)  |